三重播放時代需要的基礎設施DSP

出處:今日電子 發(fā)布于:2011-06-11 22:23:37

三重播放(Triple-play)業(yè)務是一種融合了話音、數(shù)據(jù)和視頻業(yè)務的捆綁業(yè)務模式。Triple-play業(yè)務不僅能夠滿足用戶對數(shù)據(jù)業(yè)務的需求,同時也能滿足用戶對高端業(yè)務的需求,Triple-play業(yè)務中關鍵的是以IPTV業(yè)務為代表的視頻業(yè)務。運營商提供包含視頻在內(nèi)的業(yè)務捆綁,使用戶能夠享受到業(yè)務捆綁所帶來的資費優(yōu)惠。可以提高用戶ARPU值,同時培養(yǎng)用戶的忠誠度,降低離網(wǎng)率。

三重播放的興起要求高性能與高速 IO 完美結合。本文將探討如何選擇可滿足上述要求的 DSP,提供低成本解決方案。

多媒體內(nèi)容隨著總流量的增長而變得日益豐富,這為設備制造商帶來了前所未有的工程設計挑戰(zhàn)與機遇。他們必須制造出新一代能夠處理持續(xù)急速上升的匯聚流量的設備,該匯聚流量不同于過去主導基礎局端設計范例的語音與數(shù)據(jù)流量。

這種變革是上世紀70年代計算機革命以來的多重趨勢引發(fā)的。

● 從純語音流量到語音與數(shù)據(jù)流量的轉(zhuǎn)變。這一趨勢在數(shù)十年前就已開始了,現(xiàn)在仍在繼續(xù)。

● 多媒體流量,特別是流媒體,加入現(xiàn)有的語音與數(shù)據(jù)流量。電信運營商轉(zhuǎn)向提供語音、視頻與數(shù)據(jù)服務的“三重播放業(yè)務”可充分證實這一發(fā)展趨勢。

● 從固定地址服務到家庭服務再到移動服務的演進。有線基礎局端中從語音到數(shù)據(jù)再到媒體的演進現(xiàn)在正在無線領域悄然進行。

● 上述三個趨勢推動了另一趨勢的發(fā)展:從電路交換傳輸?shù)交跀?shù)據(jù)包的傳輸?shù)难葸M,特別是對因特網(wǎng)協(xié)議(IP)流量。

在語音通信時代,電信信號處理無非是回聲消除、數(shù)據(jù)調(diào)制解調(diào)器的線路調(diào)節(jié)以及在交換電路上進行數(shù)據(jù)調(diào)制/解調(diào)的信號處理。目前,對音頻、視頻和數(shù)據(jù)流進行數(shù)字編碼/解碼以及壓縮/解壓縮的算法就有數(shù)十種之多。簡言之,電信基礎局端不僅僅是要處理更多的數(shù)據(jù),而且要實現(xiàn)信號處理量的指數(shù)級增長以實時處理大量數(shù)據(jù)。

顯然,要實現(xiàn)信號處理量的指數(shù)級增長需要大幅提高性能。一種方法是僅加快數(shù)字信號處理器(DSP)的時鐘速度。另一個根本問題是基礎局端設備采用機架安裝,對尺寸和散熱都有嚴格的要求。在機架尺寸不變(縮小尺寸除外)的情況下,高時鐘速度帶來的高散熱終也會使僅提高時鐘速度這一方法不可行。將來,電路板性能的提升會受到其功耗預算、樓宇的使用年限與位置以及安裝基礎局端設備的機架等的限制。

提高性能

電信設計工程師面臨著一個巨大的挑戰(zhàn)。他們必須在更小的板級空間內(nèi)提供更出色的性能、增加通道密度、處理日益多樣化的媒體陣列,同時保持通信的靈活性與低成本特性。

為應對這些挑戰(zhàn),DSP一直在改進。從芯片設計人員的角度,這意味著要將上述趨勢轉(zhuǎn)化為特定的 IC 特性與架構。同時實現(xiàn)高性能與低功耗目標的策略是在低電壓芯片上采用優(yōu)化的處理引擎及高效 I/O 處理盡可能多的數(shù)據(jù)。

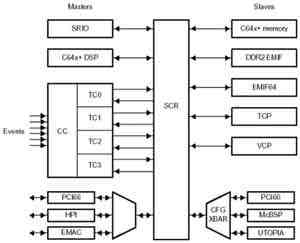

處理不斷增多的原始數(shù)據(jù)量要求極高的性能與高效的片上數(shù)據(jù)傳輸能力。從架構上講,這可通過交換中心資源 (SCR) 連接處理元件(DSP CPU、DSP 外設、協(xié)處理器加速器以及內(nèi)部存儲器)得以實現(xiàn),即具有主從單元的縱橫制架構。例如,德州儀器的TMS320C6455 DSP 采用的就是這種架構,如圖 1 所示。

圖1 TMS320C645x器件結構圖

SCR左邊的任一主單元均可直接與 SCR 右邊的從單元相連。主單元包括 DSP 的 CPU、串行高速 IO (SRIO)、四個傳輸控制器 (TC)以及將三個主外設(PCI、HPI 與 EMAC)連接至 SCR 的縱橫制端口。從單元包括 DSP 存儲器、DDR 存儲器接口、Turbo 協(xié)處理器 (TCP)、Viterbi 協(xié)處理器 (VCP) 以及將多個外設連接至 SCR 的縱橫制端口。

這種架構既快速又高效,因為 SCR 使主從單元之間實現(xiàn)了真正的同時數(shù)據(jù)傳輸。數(shù)據(jù)完全是并行傳輸。當多個主單元訪問同一個從單元時,SCR 執(zhí)行判優(yōu)。同時系統(tǒng)設計人員可以通過對主單元的優(yōu)先級別進行編程來施加某些控制。

架構要求

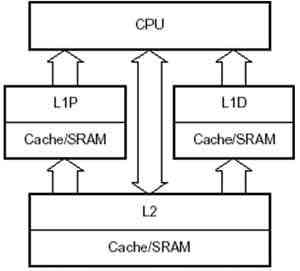

在執(zhí)行算法時,CPU與存儲器之間的指令和數(shù)據(jù)傳輸至關重要。在如圖2所示的 TMS320C6455 DSP的存儲器系統(tǒng)中,可通過使用256位寬的數(shù)據(jù)總線并在CPU與存儲器之間的內(nèi)部直接存儲器存取(DMA)架構上創(chuàng)建兩層高速緩存來優(yōu)化數(shù)據(jù)傳輸。

圖2 TMS320C64x+內(nèi)部存儲器

另一個架構要求是高效片上處理引擎。一種高效的方法是集成片上協(xié)處理器,以加速要求高性能的特定功能。例如,MS320C6455 DSP就集成了Viterbi協(xié)處理器(VCP)與Turbo協(xié)處理器 (TCP),如圖1所示。

片上處理工作完成后,開發(fā)人員仍需將大量數(shù)據(jù)從芯片傳輸至電路板上,終傳輸?shù)诫娦艂鬏斀橘|(zhì)上。顯然應選擇高速IO,但考慮到上述的異構架構,確定哪種處理方法就會變得復雜。

解決方案是為片內(nèi)板級接口提供多種高性能IO接口。SRIO是異構多處理器器件間通信的選擇,因為其高吞吐消息傳遞方案可實現(xiàn)95%的帶寬利用率。

雖然 DSP處理能力隨著具有更強并行能力以及其他特性的新架構的推出而顯著提高,但電路板設計人員還可通過將多個DSP高效集成到單個電路板來獲取更明顯的改善。使用 SRIO 快速連接大大簡化了這項工作,因為從DSP軟件的角度,DSP之間的數(shù)據(jù)流處理與單個DSP內(nèi)的數(shù)據(jù)流處理并沒有很大的差異。

板級性能

在傳統(tǒng)系統(tǒng)中,語音與數(shù)據(jù)流量是分開的,這導致了效率低下。隨著時間或其他一些影響流量配置的參數(shù)的變化,可能會出現(xiàn)處理能力與帶寬的閑置。利用新一代架構,設計人員能夠設計出在單個器件上更高效處理所有流量的系統(tǒng)。

這種融合解決方案的范例之一是Surf公司的SurfRider產(chǎn)品系列。該產(chǎn)品系列針對可優(yōu)化的低成本電路板提供軟硬件,以滿足特定系統(tǒng)流量要求。

SurfRider/AMC可在單個電路板上集成多達8個DSP,并可實現(xiàn)高達10Gb/s吞吐能力。在單個電信計算架構或MicroTCA機架上可安裝8個電路板。

發(fā)展無止境

通過在DSP內(nèi)部增加并行處理功能,并使用DSP、片外存儲器及其他組件之間的超高速互連,芯片設計人員可設計出新一代基礎局端電路板和網(wǎng)關系統(tǒng)。這些系統(tǒng)使電信營運商不僅能夠同時提供三重播放業(yè)務服務,而且還可靈活適應流量類型和負載的變化。

在單個芯片上集成多個DSP內(nèi)核的做法正在悄然興起。當前電信運營商正努力從傳統(tǒng)基礎網(wǎng)絡運營商向現(xiàn)代綜合信息服務提供商轉(zhuǎn)型,網(wǎng)絡的建設發(fā)展將是以業(yè)務為的發(fā)展模式,寬帶業(yè)務的轉(zhuǎn)型將表現(xiàn)為:多媒體、互動形態(tài)逐漸占主流的多重業(yè)務模式;基于IP的網(wǎng)絡業(yè)務融合(視頻、語音、數(shù)據(jù)融合);個性化的點對點通信(P2P)廣泛應用;用戶按需獲得充足的帶寬資源和服務。 這種業(yè)務演變趨勢對光纖接入網(wǎng)絡提出了迫切要求。

Salira EPON接入平臺是實現(xiàn)Triple-play業(yè)務的理想承載平臺,從業(yè)務支持能力、帶寬能力、QoS、安全性和網(wǎng)絡管理等各個方面對多重業(yè)務提供的保證,Salira 2000系統(tǒng)根據(jù)光纖入戶和三重播放業(yè)務模式的不斷成熟推出適合的ONU,滿足未來寬帶網(wǎng)絡發(fā)展的趨勢。

隨著電信行業(yè)邁入三重播放業(yè)務時代,其面臨著幾年前可能還無法解決的工程設計挑戰(zhàn)。對性能的要求無疑會繼續(xù)提高,但設計人員增強創(chuàng)新型DSP芯片性能的能力會隨著多核和基于DSP的SoC的興起而提高,使DSP能夠解決以前在系統(tǒng)性能、功耗、靈活性以及單通道價格等方面的難題。

版權與免責聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關法律責任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔此類作品侵權行為的直接責任及連帶責任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負版權等法律責任。

如涉及作品內(nèi)容、版權等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關權利。

- 掌握 DSP:原理剖析與應用實踐2025/5/8 14:03:24

- 模糊邏輯在 DSP 上實時執(zhí)行2023/7/25 17:13:30

- 多速率DSP及其在數(shù)模轉(zhuǎn)換中的應用2023/6/12 15:28:52

- 使用 DSP 加速 CORDIC 算法2023/3/29 15:46:30

- 高速DSP系統(tǒng)的信號完整性2022/9/26 16:45:38