針對(duì)3/3相雙繞組感應(yīng)發(fā)電機(jī)設(shè)計(jì)的勵(lì)磁系統(tǒng)

出處:電子應(yīng)用技術(shù) 發(fā)布于:2011-06-13 15:30:14

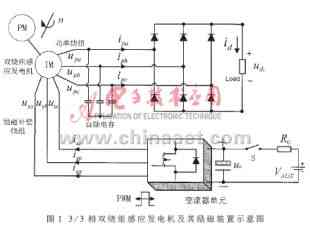

設(shè)計(jì)的勵(lì)磁系統(tǒng),由DSP和FPGA構(gòu)成。該系統(tǒng)帶有勵(lì)磁補(bǔ)償和功率這兩個(gè)繞組,如圖1所示。勵(lì)磁補(bǔ)償繞組上接一個(gè)電力電子變換裝置,用來(lái)提供感應(yīng)發(fā)電機(jī)需要的無(wú)功功率,使功率繞組上輸出一個(gè)穩(wěn)定的直流電壓。

圖1中各參數(shù)的含義如下:

isa,isb,isc——補(bǔ)償繞組中的勵(lì)磁電流;

usa,usb,usc——補(bǔ)償繞組相電壓;

ipa,ipb,ipc——功率繞組電流;

upa,upb,upc——功率繞組相電壓;

udc——二極管整流橋直流側(cè)輸出電壓;

uc——變流器直流側(cè)電容電壓。

電力電子變換裝置由功率器件及其驅(qū)動(dòng)電路和控制電路兩部分組成。功率器件選用三菱公司的智能功率模塊(IPM)PM75CSA120(75A/1200V),驅(qū)動(dòng)電路使用光耦HCPL4502。

2 EPM7128與TMS320C32同外設(shè)之間的接口電路

圖2所示為控制電路的接口電路。控制電路使用的DSP是TMS320C32,它是TI公司生產(chǎn)的第三代高性能的CMOS 32位數(shù)字信號(hào)處理器,其擁有指令系統(tǒng)強(qiáng)大,數(shù)據(jù)處理快和結(jié)構(gòu)創(chuàng)新的特點(diǎn),已經(jīng)成為理想的工業(yè)控制用DSP器件。其主要特點(diǎn)是:

(1)單周期指令執(zhí)行時(shí)間為50ns,具有每秒可執(zhí)行2200萬(wàn)條指令、進(jìn)行4000萬(wàn)次浮點(diǎn)運(yùn)算的能力;

(2)提供了一個(gè)增強(qiáng)的外部存儲(chǔ)器配置接口,具備更加靈活的存儲(chǔ)器管理與數(shù)據(jù)處理方式。

控制電路使用的FPGA器件為ALTERA公司的EPM7128,它屬于高密度、高性能的CMOS EPLD器件,與ALTERA公司的MAXPLUS II開(kāi)發(fā)系統(tǒng)軟件配合,可以100%地模仿高密度的集成有各種邏輯函數(shù)和多種可編程邏輯的TTL器件。采用類(lèi)似器件作為DSP的專(zhuān)用外圍集成電路(ASIC)更為經(jīng)濟(jì)靈活,可以進(jìn)一步降低控制系統(tǒng)的成本。

電壓檢測(cè)使用三相變壓器,電流檢測(cè)使用HL電流傳感器。電平轉(zhuǎn)換電路用來(lái)將檢測(cè)到的信號(hào)轉(zhuǎn)換為0~5V的電平。A/D轉(zhuǎn)換器選用ADS7862。保護(hù)電路使用電壓比較器311得到過(guò)壓/過(guò)流故障信號(hào)。

DSP完成以下四項(xiàng)工作:

◆數(shù)據(jù)的采集和處理

◆控制算法的完成

◆PWM脈沖值的計(jì)算

◆保護(hù)中斷的處理

FPGA完成以下三項(xiàng)工作:

(1)管理DSP和各種外部設(shè)備的接口;

(2)脈沖的輸出和死區(qū)的產(chǎn)生;

(3)保護(hù)信號(hào)的處理。

3 使用FPGA實(shí)現(xiàn)DSP和ADS7862之間的高速接口

ADS7862是TI公司專(zhuān)為電機(jī)和電力系統(tǒng)控制而設(shè)計(jì)的A/D轉(zhuǎn)換器。它的主要特點(diǎn)有:

◆4個(gè)全差分輸入接口,可分成兩組,兩個(gè)通道可同時(shí)轉(zhuǎn)換

◆12bits并行輸出

◆每通道的轉(zhuǎn)換速率為500kHz

控制方法為:

◆由A0線的值決定哪兩個(gè)通道轉(zhuǎn)換

◆由Convst線上的脈寬大于250ns的低電平脈沖啟動(dòng)轉(zhuǎn)換

◆由CS和RD線的低電平控制數(shù)據(jù)的讀出,連續(xù)兩次讀信號(hào)可以得到兩個(gè)通道的數(shù)據(jù)

系統(tǒng)中使用了兩片ADS7862,它們的控制線使用同樣的接口,數(shù)據(jù)線則分別和DSP的高/低16位數(shù)據(jù)線中的低12位相連接。這樣DSP可以同時(shí)控制兩片A/D轉(zhuǎn)換器:4通道同時(shí)轉(zhuǎn)換;每次讀操作可以得到兩路數(shù)據(jù)。

如圖3所示,將A/D轉(zhuǎn)換器的控制信號(hào)映射為DSP的三個(gè)外部端口:A0、ADCS(和ADRD使用一個(gè)端口)和CONVST。在FPGA中使用邏輯譯碼器對(duì)端口譯碼。利用AHDL語(yǔ)言編寫(xiě)的譯碼程序如下:

TABLE

A[2312],IS,RW=>A0,ADCS,CONVST,PWM1,PWM2,

PWM3, PWM, PRO, CLEAR;

H″810″,0,0=>0,1,1,1,1,1,1,1,1;

H″811″,0,1=>1,0,1,1,1,1,1,1,1;

H″812″,0,0=>1,1,0,1,1,1,1,1,1;

H″813″,0,1=>1,1,1,0,1,1,1,1,1;

H″814″,0,0=>1,1,1,1,0,1,1,1,1;

H″815″,0,0=>1,1,1,1,1,0,1,1,1;

H″816″,0,0=>1,1,1,1,1,1,0,1,1;

H″817″,0,1=>1,1,1,1,1,1,1,0,1;

H″817″,0,0=>1,1,1,1,1,1,1,1,0;

END TABLE

其中,0表示低電平,1表示高電平。RW=1表示讀,RW=0表示寫(xiě)。

DSP對(duì)這三個(gè)端口進(jìn)行操作就可以控制A/D轉(zhuǎn)換器:

(1)寫(xiě)CONVST端口可以啟動(dòng)A/D轉(zhuǎn)換器;

(2)讀ADCS端口可以從A/D轉(zhuǎn)換器中讀到數(shù)據(jù);

(3)寫(xiě)數(shù)據(jù)到A0端口可以設(shè)置不同的通道。

使用上述方法可以實(shí)現(xiàn)DSP和A/D轉(zhuǎn)換器之間的無(wú)縫快速連接。

4 使用FPGA實(shí)現(xiàn)PWM脈沖的產(chǎn)生和死區(qū)的注入

FPGA除了管理DSP和外設(shè)的接口外,還完成PWM脈沖的產(chǎn)生和死區(qū)的注入。將PWM芯片和死區(qū)發(fā)生器集成在FPGA中,就可以使DSP專(zhuān)注于復(fù)雜算法的實(shí)現(xiàn),而將PWM處理交給FPGA系統(tǒng),使系統(tǒng)運(yùn)行于準(zhǔn)并行處理狀態(tài)。

5 使用FPGA實(shí)現(xiàn)系統(tǒng)保護(hù)

為了保護(hù)發(fā)電機(jī)和IGBT功率器件,勵(lì)磁控制系統(tǒng)提供了多種保護(hù)功能:

◆變流器直流側(cè)過(guò)壓保護(hù)

◆變流器交流電流過(guò)流保護(hù)

◆變流器過(guò)溫保護(hù)

◆發(fā)電機(jī)輸出過(guò)壓保護(hù)

◆IPM錯(cuò)誤保護(hù)

使用如圖4所示的硬件邏輯來(lái)實(shí)現(xiàn)保護(hù)功能。當(dāng)FPGA檢測(cè)到相應(yīng)的故障信號(hào)時(shí),D觸發(fā)器輸出一個(gè)錯(cuò)誤信號(hào),使與門(mén)輸出一個(gè)低電平,此低電平封鎖住所有的PWM脈沖,并觸發(fā)一個(gè)DSP的外部中斷信號(hào)。當(dāng)DSP響應(yīng)外部中斷時(shí),可以使用PRO端口讀到錯(cuò)誤的狀態(tài)位。CLEAR端口用來(lái)清除D觸發(fā)器,系統(tǒng)因此可以重復(fù)啟動(dòng)。

圖5給出了本控制系統(tǒng)的實(shí)驗(yàn)波形圖:變流器的輸出電流基本為正弦;變流器側(cè)電容電壓穩(wěn)定在365V;功率繞組側(cè)輸出電壓穩(wěn)定在510V。

關(guān)于Altera 公司

Altera 公司 (NASDAQ:ALTR) 秉承了創(chuàng)新的傳統(tǒng),是世界上“可編程芯片系統(tǒng)” (SOPC) 解決方案倡導(dǎo)者。Altera 公司總部位于美國(guó)加州的圣何塞,并在的14個(gè)國(guó)家中擁有近2000名員工,其2005年度的年收入高達(dá)11.23億美元。Altera 將其早在1983年發(fā)明的可編程邏輯技術(shù)與軟件工具、IP 和設(shè)計(jì)服務(wù)相結(jié)合,向全世界近14,000家客戶(hù)提供超值的可編程解決方案。

關(guān)于TI

德州儀器 (Texas Instruments),簡(jiǎn)稱(chēng)TI,是的半導(dǎo)體公司,為現(xiàn)實(shí)世界的信號(hào)處理提供創(chuàng)新的數(shù)字信號(hào)處理(DSP)及模擬器件技術(shù)。除半導(dǎo)體業(yè)務(wù)外,還提供包括傳感與控制、教育產(chǎn)品和數(shù)字光源處理解決方案。TI總部位于美國(guó)得克薩斯州的達(dá)拉斯,并在25多個(gè)國(guó)家設(shè)有制造、設(shè)計(jì)或銷(xiāo)售機(jī)構(gòu)。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫(kù)電子市場(chǎng)網(wǎng)”的所有作品,版權(quán)均屬于維庫(kù)電子市場(chǎng)網(wǎng),轉(zhuǎn)載請(qǐng)必須注明維庫(kù)電子市場(chǎng)網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類(lèi)作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問(wèn)題,請(qǐng)?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- 掌握 DSP:原理剖析與應(yīng)用實(shí)踐2025/5/8 14:03:24

- 模糊邏輯在 DSP 上實(shí)時(shí)執(zhí)行2023/7/25 17:13:30

- 多速率DSP及其在數(shù)模轉(zhuǎn)換中的應(yīng)用2023/6/12 15:28:52

- 使用 DSP 加速 CORDIC 算法2023/3/29 15:46:30

- 高速DSP系統(tǒng)的信號(hào)完整性2022/9/26 16:45:38

- 編碼器的工作原理及作用1

- 超強(qiáng)整理!PCB設(shè)計(jì)之電流與線寬的關(guān)系2

- 三星(SAMSUNG)貼片電容規(guī)格對(duì)照表3

- 電腦藍(lán)屏代碼大全4

- 國(guó)標(biāo)委發(fā)布《電動(dòng)汽車(chē)安全要求第3部分:人員觸電防護(hù)》第1號(hào)修改單5

- 通俗易懂談上拉電阻與下拉電阻6

- 繼電器的工作原理以及驅(qū)動(dòng)電路7

- 電容單位8

- 跟我學(xué)51單片機(jī)(三):?jiǎn)纹瑱C(jī)串口通信實(shí)例9

- 一種三極管開(kāi)關(guān)電路設(shè)計(jì)10

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號(hào)完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車(chē)電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號(hào)鏈中的濾波與功耗管理