合眾達(dá)發(fā)布基于DM6727高性能音頻開發(fā)平臺SEED-ADK6727

出處:電子工程世界 發(fā)布于:2011-06-03 17:48:38

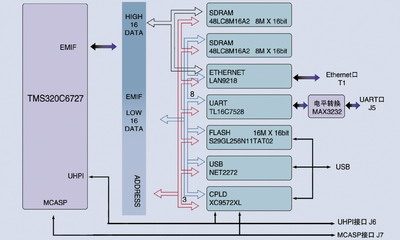

近日合眾達(dá)電子發(fā)布高性能音頻DSF開發(fā)套件SEED-ADK6727,SEED-ADK6727采用TI新-代推出的性價(jià)比DSP TMS320C6727(工作主頻達(dá)到300MHz),能廣泛應(yīng)用于高性能的音頻處理系統(tǒng)、醫(yī)療、音頻算法評估、工業(yè)的音頻產(chǎn)品:音頻會(huì)議、音頻廣播等領(lǐng)域。 美國國家儀器有限公司(National Instruments,簡稱NI)近日推出行業(yè)內(nèi)首款應(yīng)用于PXI系統(tǒng)的3U四核嵌入式控制器--PXI 8110嵌人式控制器,它配備了2.26GHz的Intel Core 2 Q9100四核處理器,可支持4GB 800 MHz DDR2內(nèi)存以及高性能的7200轉(zhuǎn)硬盤驅(qū)動(dòng)器,可以說是行業(yè)內(nèi)3UPXI系列中性能強(qiáng)勁的嵌入式控制器。

SEED-ADK6727外觀圖

特點(diǎn):

1、TI新一代的性價(jià)比的浮點(diǎn)DSP:TMS320C6727,C67x+ DSP核,工作主頻達(dá)

到300MHz,1800MFLOPS運(yùn)算能力。

2、片上存儲資源:

32K-Byte Program Cache

256K-Byte SRAM

DDR2 SDRAM:外擴(kuò)8M x 32bit 的SDRAM

Flash:外擴(kuò)16M x 16bit的Flash

dMAX支持:Dual Data Movement Accelerator

套件包含主板SEED-ADK6727和擴(kuò)展板SEED-AIM6727

接口:

1、1個(gè)32位的EMIF存儲器訪問接口,1個(gè)UHPI接口,2路I2C,2個(gè)SPI接口

2、3路McASP多通道音頻串口

3、1路標(biāo)準(zhǔn)的USB2.0接口

4、1個(gè)10/100Mbps以太網(wǎng)接口

5、1路RS232 UART串口

6、8路模擬信號輸入和輸出接口

7、1路數(shù)字音頻光信號輸入和輸出接口

8、1路數(shù)字音頻電信號輸入和輸出接口

9、1路MIDI輸入和輸出接口

SEED-ADK6727原理框圖

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- 掌握 DSP:原理剖析與應(yīng)用實(shí)踐2025/5/8 14:03:24

- 模糊邏輯在 DSP 上實(shí)時(shí)執(zhí)行2023/7/25 17:13:30

- 多速率DSP及其在數(shù)模轉(zhuǎn)換中的應(yīng)用2023/6/12 15:28:52

- 使用 DSP 加速 CORDIC 算法2023/3/29 15:46:30

- 高速DSP系統(tǒng)的信號完整性2022/9/26 16:45:38

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號鏈中的濾波與功耗管理