簡便的包含嵌入式存儲器的FPGA結(jié)構(gòu)實(shí)現(xiàn)

出處:段會福,周華兵 發(fā)布于:2011-09-02 12:16:54

1.引言

傳統(tǒng)上 FPGA只能實(shí)現(xiàn)相對較小的邏輯電路,隨著工藝技術(shù)的提高,F(xiàn)PGA的容量和性能也不斷提高,F(xiàn)PGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。目前以硬件描述語言(Verilog 或 VHDL)所完成的電路設(shè)計(jì),可以經(jīng)過簡單的綜合與布局,快速的燒錄至 FPGA 上進(jìn)行測試,是現(xiàn)代 IC 設(shè)計(jì)驗(yàn)證的技術(shù)主流。這些可編輯元件可以被用來實(shí)現(xiàn)一些基本的邏輯門電路(比如AND、OR、XOR、NOT)或者更復(fù)雜一些的組合功能比如解碼器或數(shù)學(xué)方程式。在大多數(shù)的FPGA里面,這些可編輯的元件里也包含記憶元件例如觸發(fā)器(Flip-flop)或者其他更加完整的記憶塊。

然而,多數(shù)學(xué)術(shù)性的 FPGA CAD工具只針對于同質(zhì)的 FPGA,即只包含邏輯模塊和布線資源的 FPGA。本文中我們提出了一種靈活的包含嵌入式存儲器的 FPGA的結(jié)構(gòu)以及一種建立RRG(布線資源圖)的方法。FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個(gè)概念,內(nèi)部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內(nèi)部連線(Interconnect)三個(gè)部分。 現(xiàn)場可編程門陣列(FPGA)是可編程器件。與傳統(tǒng)邏輯電路和門陣列(如PAL,GAL及CPLD器件)相比,F(xiàn)PGA具有不同的結(jié)構(gòu),F(xiàn)PGA利用小型查找表(16×1RAM)來實(shí)現(xiàn)組合邏輯,每個(gè)查找表連接到一個(gè)D觸發(fā)器的輸入端,觸發(fā)器再來驅(qū)動其他邏輯電路或驅(qū)動I/O,由此構(gòu)成了即可實(shí)現(xiàn)組合邏輯功能又可實(shí)現(xiàn)時(shí)序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內(nèi)部靜態(tài)存儲單元加載編程數(shù)據(jù)來實(shí)現(xiàn)的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及個(gè)模塊之間或模塊與I/O間的連接方式,并終決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并終決定了FPGA所能實(shí)現(xiàn)的功能, FPGA允許無限次的編程。

2.結(jié)構(gòu)

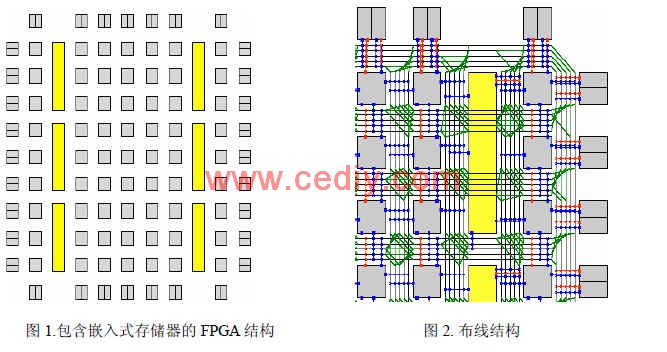

包含嵌入式存儲器的FPGA結(jié)構(gòu)如圖1所示。整個(gè) FPGA由四種基本資源構(gòu)成,邏輯模塊,I/O模塊,布局布線模塊和存儲器模塊。每個(gè)存儲器模塊的存儲容量是固定的,但是用戶可以對存儲器模塊進(jìn)行配置,以實(shí)現(xiàn)不同長寬比的存儲器。我們假設(shè)存儲器模塊在整個(gè) FPGA芯片中按列排放。存儲器模塊的列數(shù),每列存儲器所處的位置、每列存儲器模塊包含的存儲器模塊數(shù)目以及每列存儲器模塊中個(gè)存儲器模塊的起始物理位置都會在結(jié)構(gòu)描述文件中定義。

圖 2所示為我們的 FPGA布線結(jié)構(gòu),這是一種島式結(jié)構(gòu)。邏輯模塊周圍圍繞了布線通道。每個(gè)邏輯模塊的輸入或輸出引腳可以通過一個(gè)由可配置開關(guān)組成的連接模塊與靠近它的通道中的 8條連線相連。在每一個(gè)垂直通道和水平通道交叉處有一個(gè)開關(guān)模塊。開關(guān)模塊給每條輸入信號線提供了三個(gè)可能的連接選擇。同邏輯模塊相同,存儲器模塊也通過連接模塊與邏輯布線相連。在圖 2中的結(jié)構(gòu)中, Fm=3。Fm的值是 1,值為 V,這里的 V值即每個(gè)布線通道中的連線數(shù)目。

3.具體實(shí)現(xiàn)方式

存儲器模塊相對于邏輯模塊,有一些不同之處,例如模塊引腳的分布方式、模塊高度等,這使得 RRG的設(shè)計(jì)非常復(fù)雜。在這一部分中,我們將討論一種簡單而且靈活的 RRG設(shè)計(jì)方法。

3.1結(jié)構(gòu)描述

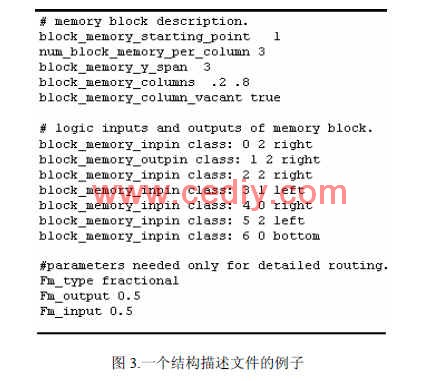

VPR用布線結(jié)構(gòu)描述語言定義 FPGA的布線結(jié)構(gòu)【 5】。VPR通過一個(gè)內(nèi)部的“結(jié)構(gòu)產(chǎn)生器”來產(chǎn)生 RRG。我們擴(kuò)展了布線結(jié)構(gòu)描述語言來定義包含嵌入式存儲器的FPGA的布線結(jié)構(gòu),然后我們改進(jìn)了 VPR的結(jié)構(gòu)產(chǎn)生器以適應(yīng)這些擴(kuò)展。

由于嵌入式存儲器模塊的存在,我們對布線結(jié)構(gòu)描述語言的擴(kuò)展主要包括:(1)存儲器模塊的列數(shù),(2)每列存儲器模塊的相對位置,(3)存儲器模塊輸入和輸出引腳的 Fm值,(4)每列存儲器模塊中的存儲器模塊數(shù)目,(5)每列存儲器模塊中個(gè)存儲器模塊的起始位置,(6)存儲器模塊的高度,(7)存儲器模塊輸入輸出引腳的數(shù)目,(8)存儲器模塊每個(gè)輸入或輸出引腳對應(yīng)的邊( side)和群( cluster),例如如圖 2所示的 FPGA結(jié)構(gòu)中,存儲器模塊的左邊和右邊共有 3個(gè)群,因?yàn)榇鎯ζ髂K的高度是 3個(gè)邏輯模塊的高度,而上下兩邊只有一個(gè)群。(9)每個(gè)存儲器模塊中的組合邏輯電路延遲和時(shí)序電路延時(shí)。

圖 3所示為一個(gè)描述包含嵌入式存儲器的 FPGA布線結(jié)構(gòu)的文件的一部分,其中邏輯模塊由一個(gè) 4輸入的查找表和一個(gè)寄存器構(gòu)成。圖 1和圖 2示出了這種 FPGA的結(jié)構(gòu)。VA產(chǎn)生的文件要滿足圖 3定義的結(jié)構(gòu),其中需要的布線通道寬度為 5,即 5條連線。這些描述 FPGA結(jié)構(gòu)的圖形都是由我們的 VA產(chǎn)生。圖 1示出了整個(gè) FPGA的結(jié)構(gòu),這種情況下,整個(gè) FPGA包含 9x9個(gè)邏輯模塊,周圍圍繞 I/O模塊。黃色所示的為兩列存儲器模塊,每個(gè)存儲器模塊跨越 3個(gè)邏輯模塊的高度。圖 2所示僅為FPGA近距離結(jié)構(gòu)的一部分。

3.2布線資源圖

雖然上述所列的結(jié)構(gòu)參數(shù)使得 FPGA的結(jié)構(gòu)很容易就可以定義,但是對于布線器來說它并不是一個(gè)合適的表達(dá)方法。在 RRG中,連線、邏輯模塊的引腳以及存儲器模塊的引腳都被表示為節(jié)點(diǎn),開關(guān)被表示為連接兩個(gè)節(jié)點(diǎn)的邊。

如前所述,我們對 VPR的結(jié)構(gòu)產(chǎn)生器作了改進(jìn)以建立包含嵌入式存儲器的 FPGA的 RRG。由于存儲器模塊在 Y方向跨越多個(gè)邏輯模塊,這就使得在 RRG中插入存儲器模塊的引腳變得復(fù)雜,同時(shí)連接從存儲器模塊輸出引腳到連線以及從連線到存儲器輸入引腳的邊也更加復(fù)雜。但幸運(yùn)的是如圖 2所示,存儲器模塊的存在并不破壞布線通道的分布。為了方便建立 RRG,我們增加了虛構(gòu)存儲器模塊的定義,在建立 RRG的過程中,存儲器模塊的位置由它的起始位置來表示。當(dāng)在建立 RRG對所有模塊進(jìn)行掃描的時(shí)候,我們對存儲器模塊以及虛構(gòu)存儲器模塊的處理方法和對邏輯塊的處理方法是一樣的。通過這樣的方法,我們簡化了創(chuàng)建異質(zhì) FPGA布線資源圖的過程。

4.結(jié)論

本文中,我們提出了一種包含嵌入式存儲器的 FPGA的靈活結(jié)構(gòu)以及一種建立 RRG的簡化方法。我們對 VPR進(jìn)行了改進(jìn),擴(kuò)展了其功能,使得它可以處理包含嵌入式存儲器的 FPGA結(jié)構(gòu),同時(shí)保持了原有的靈活性。

縱觀整個(gè)工作,我們著重處理包含嵌入式存儲器模塊的 FPGA結(jié)構(gòu),我們假設(shè)存儲器模塊按列排放。我們的這種結(jié)構(gòu)不僅適用于存儲器模塊,同時(shí)也適用于其他的按列排放的功能模塊,例如 Spartan-3系列 FPGA中的乘法器模塊以及 Stratix系列 FPGA中的 DSP模塊。

本文作者創(chuàng)新觀點(diǎn):本文中,我們提出了一種靈活的包含嵌入式存儲器的 FPGA結(jié)構(gòu)以及一種建立 RRG的簡化方法。我們對 VPR進(jìn)行了改進(jìn),擴(kuò)展了其功能,使得它可以處理包含嵌入式存儲器的 FPGA結(jié)構(gòu),同時(shí)保持了原有的靈活性。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- ARM技術(shù)架構(gòu)與應(yīng)用開發(fā)實(shí)踐指南2026/1/6 10:40:19

- 嵌入式實(shí)時(shí)操作系統(tǒng)(RTOS)選型與移植技術(shù)指南2025/12/31 10:42:31

- 工業(yè)嵌入式系統(tǒng):通信接口技術(shù)選型與抗干擾設(shè)計(jì)實(shí)踐2025/12/15 14:36:53

- 深入解析嵌入式 OPENAMP 框架:開啟異核通信新時(shí)代2025/7/22 16:27:29

- 一文快速了解OPENWRT基礎(chǔ)知識2025/7/14 16:59:04

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號鏈中的濾波與功耗管理