淺談嵌入式系統(tǒng)的VGA接口設(shè)計(jì)

出處:王瑛 盧修文 王超亮 發(fā)布于:2011-09-02 13:52:15

引言

隨著液晶技術(shù)的日益成熟,液晶顯示器在顯示技術(shù)中得到了越來越廣泛的應(yīng)用。當(dāng)前LCD顯示技術(shù)已經(jīng)成為新一代平板技術(shù)顯示技術(shù)的主流。LCD顯示屏幕主要包括液晶屏幕,驅(qū)動電路以及控制驅(qū)動電路的系統(tǒng)。我們設(shè)計(jì)的LCD控制器主要是用來控制RGB模式的數(shù)據(jù)以及MCU模式的命令,參數(shù)的傳輸,實(shí)現(xiàn)LCD的控制功能。 RGB模式主要有16bit輸入,16bit輸出; 16bit輸入,18bit輸出; 18bit輸入,16bit輸出;18bit輸入,18bit輸出;4種模式的傳輸。本文就LCD的驅(qū)動進(jìn)行分析,介紹,提出硬件電路的設(shè)計(jì)以及驗(yàn)證方法。

LCD接口轉(zhuǎn)換為VGA接口

VGA (Video Graphics Array)接口信號為模擬信號。其關(guān)鍵信號有5個,分別是Horizontal Sync水平同步信號(也叫行同步信號),垂直同步信號Vertical Sync(也叫場同步信號),Red紅色,Green 綠色和Blue 藍(lán)色。電子槍從左至右,從上至下地進(jìn)行掃描,每行結(jié)束時,用行同步信號進(jìn)行同步;掃描完所有行后用場同步信號進(jìn)行場同步。LCD接口轉(zhuǎn)VGA(簡稱LCD2VGA)是一款以FPGA 做為橋接芯片,集成高效顯存技術(shù)的視頻轉(zhuǎn)換卡。不同于簡易的D/A轉(zhuǎn)換模式,LCD2VGA上的FPGA能夠自動將LCD接口提供的刷新頻率提高到CRT顯示器所需要的高刷新頻率,解決了簡易的D/A轉(zhuǎn)換模式下屏幕閃動的問題。帶有LCD控制器的CPU 通過此視頻卡,可以驅(qū)動帶VGA 接口的液晶顯示器或CRT 顯示器。LCD2VGA能夠支持16bppTFT(真彩)型數(shù)字LCD接口向VGA接口的轉(zhuǎn)換,兼容640×480、800×600、1024×768三種分辨率,支持輸出60Hz刷新率;其工作方式和工作時序與TFT(真彩)LCD 完全一樣。

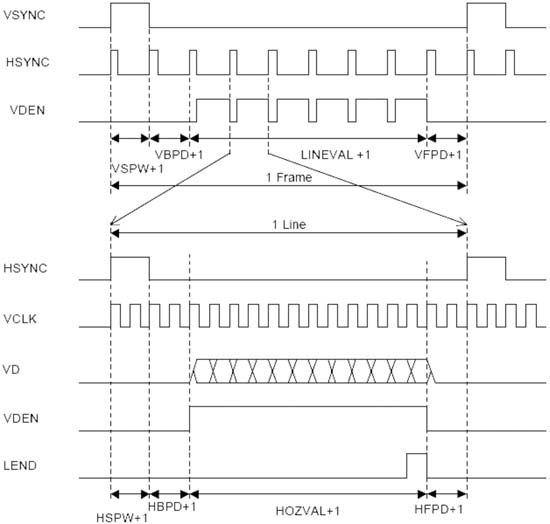

掃描式LCD接口(以S3C2410A的LCD控制器為例圖1),在每一場完畢后,也是用VSYNC來進(jìn)行場同步;每一行完畢后,也是用HSYNC進(jìn)行行同步;也有VCLK像素時鐘,用于鎖存數(shù)據(jù);

其場同步信號,寬度為(VSPW+1),之前有場消隱前肩(VFPD+1),之后有場消隱后肩(VBPD+1);

其行同步信號,寬度為(HSPW+1),之前有行消隱前肩(HFPD+1),之后有場消隱后肩(HBPD+1);

可以發(fā)現(xiàn),掃描式LCD接口的同步信號時序和VGA接口是一致的。原因是發(fā)明LCD后,盡管顯示原理不同,但為了在時序上和CRT兼容,也采用了這樣的控制時序。基于此,完將LCD接口轉(zhuǎn)換為VGA接口。

圖1 三星S3C2410A的LCD信號時序圖

方案實(shí)現(xiàn)

VGA接口只需Hsync和Vsync兩個同步信號和RGB三個色彩分量信號。而掃描式LCD接口的同步信號的時序和VGA接口的完全一致,可直接把兩個同步信號接入VGA接口。

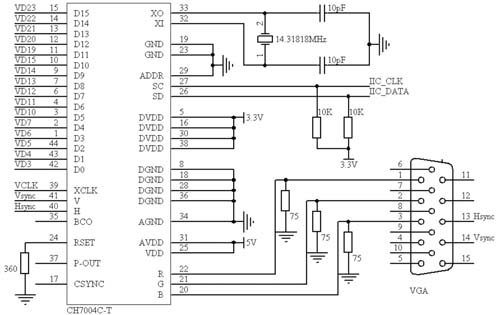

S3C2410A的LCD控制器輸出的是RGB數(shù)字信號。因此若用一些DAC芯片把RGB數(shù)字信號轉(zhuǎn)換為模擬信號,即可實(shí)現(xiàn)VGA接口的RGB信號輸入。這類視頻專用DAC芯片較多,例如ADI公司的ADV7120;CHRONTEL公司的CH7004C.實(shí)驗(yàn)中選用的CHRONTEL公司的CH7004C.S3C2410A的LCD控制器與CH7004C的連接如表1.

表1 S3C2410A的LCD控制器與CH7004C的連接

在選擇數(shù)據(jù)格式時,RGB565較合適,因?yàn)?6位數(shù)據(jù)已經(jīng)有6.5萬色,完全足夠;24位數(shù)據(jù)時每個像素實(shí)際占用32位,4個字節(jié),傳輸時對S3C2410A的總線資源占用太大。

整個電路原理圖如圖2所示。其中一些需要注意的地方有:

CH7004C工作在從模式下,由S3C2410A的I2C控制。在實(shí)驗(yàn)中使用的是較好的日本村田(murata)的阻容元件,包括10K,360歐,75歐和10pF的電容。10K用于I2C總線的上拉,360歐用于RSET引腳接地;75歐為R,G,B三個輸出管腳和地之間的終端電阻,10pF電容用于晶振。另外,CH7004C的IIC地址,是通過把ADDR引腳拉高或拉低來設(shè)定;接地時,根據(jù)芯片手冊,其7位的I2C地址為1110110,加一個讀/寫位。

圖2 CH7004C的電路原理圖

CH7004C的關(guān)鍵寄存器及設(shè)置

CH7004C片內(nèi)有25個寄存器。寄存器是中央處理器內(nèi)的組成部分。寄存器是有限存貯容量的高速存貯部件,它們可用來暫存指令、數(shù)據(jù)和位址。在中央處理器的控制部件中,包含的寄存器有指令寄存器(IR)和程序計(jì)數(shù)器(PC)。在中央處理器的算術(shù)及邏輯部件中,包含的寄存器有累加器(ACC)。寄存器的功能十分重要,CPU對存儲器中的數(shù)據(jù)進(jìn)行處理時,往往先把數(shù)據(jù)取到內(nèi)部寄存器中,而后再作處理。外部寄存器是計(jì)算機(jī)中其它一些部件上用于暫存數(shù)據(jù)的寄存器,它與CPU之間通過"端口"交換數(shù)據(jù),外部寄存器具有寄存器和內(nèi)存儲器雙重特點(diǎn)。有些時候我們常把外部寄存器就稱為"端口",這種說法不太嚴(yán)格,但經(jīng)常這樣說。其中比較關(guān)鍵的是Display Mode,Input Data Format,Sync Polarity三個寄存器。Display Mode顯示模式寄存器,片內(nèi)地址0X00,輸入分辨率為640×480,由芯片手冊,可選模式從Mode13到Mode17均可。實(shí)驗(yàn)中選擇的是默認(rèn)的Mode17,對應(yīng)參數(shù)為0X6A.Input Data Format輸入數(shù)據(jù)格式寄存器,片內(nèi)地址是0X04,因?yàn)檩斎氲臄?shù)據(jù)格式為RGB565,且需打開pass-through模式,故對應(yīng)參數(shù)為0X20.Sync Polarity同步信號極性寄存器,片內(nèi)地址0X0D,根據(jù)輸入的Hsync和Vsync的極性來設(shè)定,如果是均為負(fù)脈沖,則把VSP位和HSP位都置0;如果均為正脈沖,則把VSP位和HSP位都設(shè)置為1.實(shí)驗(yàn)中,把S3C2410A的LCD控制器的同步信號極性均設(shè)為低電平有效,故參數(shù)為0X00.

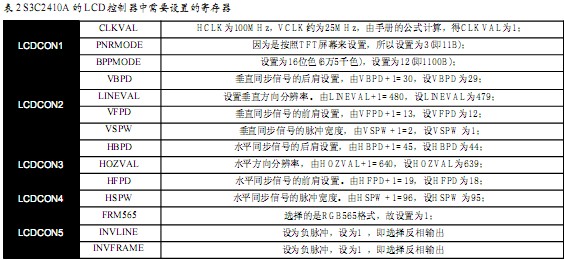

S3C2410A的LCD控制器設(shè)置

作為輸出源,S3C2410A的LCD控制器也需要進(jìn)行相應(yīng)設(shè)置。需要的輸出分辨率是640×480,16位色(RGB565格式),刷新率60Hz.一共有LCDCON1到LCDCON5共5個寄存器需要設(shè)置,具體參數(shù)要參考VGA時序規(guī)范和LCD時序圖(圖1)。所需設(shè)置的寄存器如表2.

表2 S3C2410A的LCD控制器中需要設(shè)置的寄存器

S3C2410A的LCD控制器設(shè)置

實(shí)驗(yàn)及數(shù)據(jù)

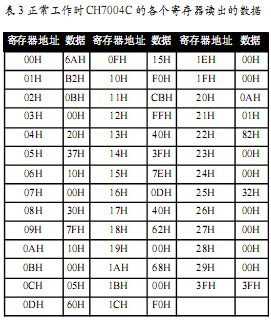

實(shí)驗(yàn)中,選擇的操作系統(tǒng)嵌入式Linux,內(nèi)核版本2.4.18,圖形系統(tǒng)是Qtopia 1.7.0.bootloader選用的韓國MIZI公司的vivi.上電后,vivi將進(jìn)行初始化,其中包括設(shè)置CH7004,然后再引導(dǎo)進(jìn)入Linux.對CH7004的操作,完全可以看作對一個IIC接口的EEPROM來進(jìn)行,即I2C,一種總線結(jié)構(gòu)。IIC 是作為英特爾IC 的互補(bǔ),這種總線類型是由菲利浦半導(dǎo)體公司在八十年代初設(shè)計(jì)出來的,主要是用來連接整體電路(ICS) ,IIC是一種多向控制總線,也就是說多個芯片可以連接到同一總線結(jié)構(gòu)下,同時每個芯片都可以作為實(shí)施數(shù)據(jù)傳輸?shù)目刂圃础_@種方式簡化了信號傳輸總線。例如:內(nèi)存中的SPD信息,通過IIC,與BX芯片組聯(lián)系,IIC 存在于英特爾PIIX4結(jié)構(gòu)體系中。可專門定義一個函數(shù)IIC_Write()來寫數(shù)據(jù)。例如對IDF寄存器的設(shè)置為I2C_Write(0xec,0x04,0x20)。設(shè)置好后,CH7004的所有寄存器數(shù)據(jù)如表3.

實(shí)驗(yàn)中還發(fā)現(xiàn),設(shè)定SPR同步信號極性寄存器時,如果都設(shè)同步信號為正脈沖有效,接顯示器也能正常顯示,但是有閃爍。負(fù)脈沖有效則無這種情況,故推薦均設(shè)置為負(fù)脈沖有效。

表3 正常工作時,CH7004C的各個寄存器讀出的數(shù)據(jù)

結(jié)語

本文提供的LCD接口轉(zhuǎn)換為VGA接口的解決方案,經(jīng)過實(shí)際驗(yàn)證,切實(shí)可行。在Linux和Windows CE 4.2兩種嵌入式操作系統(tǒng)下均進(jìn)行了測試,Linux是一類Unix計(jì)算機(jī)操作系統(tǒng)的統(tǒng)稱。Linux操作系統(tǒng)的內(nèi)核的名字也是"Linux".Linux操作系統(tǒng)也是自由軟件和開放源代碼發(fā)展中著名的例子。嚴(yán)格來講,Linux這個詞本身只表示Linux內(nèi)核,但在實(shí)際上人們已經(jīng)習(xí)慣了用Linux來形容整個基于Linux內(nèi)核,并且使用GNU 工程各種工具和數(shù)據(jù)庫的操作系統(tǒng)。Linux得名于計(jì)算機(jī)業(yè)余愛好者Linus Torvalds.Linux下VGA顯示器的畫面非常穩(wěn)定;在Windows CE 4.2下基本穩(wěn)定,略有閃爍。該方案特點(diǎn)在于讓嵌入式系統(tǒng)直接支持VGA顯示器,具備較大的實(shí)際應(yīng)用意義。

圖3 Linux下外接VGA顯示器

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- ARM技術(shù)架構(gòu)與應(yīng)用開發(fā)實(shí)踐指南2026/1/6 10:40:19

- 嵌入式實(shí)時操作系統(tǒng)(RTOS)選型與移植技術(shù)指南2025/12/31 10:42:31

- 工業(yè)嵌入式系統(tǒng):通信接口技術(shù)選型與抗干擾設(shè)計(jì)實(shí)踐2025/12/15 14:36:53

- 深入解析嵌入式 OPENAMP 框架:開啟異核通信新時代2025/7/22 16:27:29

- 一文快速了解OPENWRT基礎(chǔ)知識2025/7/14 16:59:04

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號鏈中的濾波與功耗管理