FPGA和單片機(jī)的頻率監(jiān)測系統(tǒng)實現(xiàn)

出處:czhlcai 發(fā)布于:2011-09-04 20:38:24

本系統(tǒng)利用單片機(jī)和FPGA有效的結(jié)合起來共同實現(xiàn)等頻率測量和IDDS技術(shù),發(fā)揮各自的優(yōu)點,使設(shè)計變得更加容易和靈活,并具有頻率測量范圍寬、產(chǎn)生的波形頻率分辨率高及大等特點。

FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。

系統(tǒng)方便靈活,測量和產(chǎn)生的波形分辨率高,能適應(yīng)當(dāng)代許多高測量和波形產(chǎn)生的要求,可以在各類測量系統(tǒng)和信號發(fā)生器中得到很好的利用,頻率測量在電路實驗、通訊設(shè)備、音頻視頻和科學(xué)研究中具有十分廣泛的用途。

1.DDS信號發(fā)生器的實現(xiàn)

DDS同 DSP(數(shù)字信號處理)一樣,是一項關(guān)鍵的數(shù)字化技術(shù)。DDS是直接數(shù)字式頻率合成器(Direct Digital Synthesizer)的英文縮寫。與傳統(tǒng)的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉(zhuǎn)換時間等優(yōu)點,廣泛使用在電信與電子儀器領(lǐng)域,是實現(xiàn)設(shè)備全數(shù)字化的一個關(guān)鍵技術(shù)。

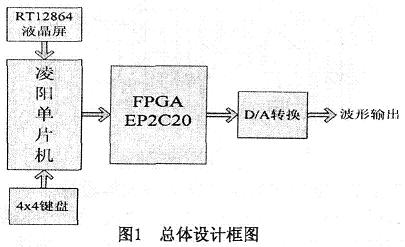

使用FPGA與單片機(jī)相結(jié)合的方式構(gòu)成DDS信號發(fā)生器的部分,其中FPGA完成相位累加、波形地址查找及波形輸出等功能,凌陽16位單片機(jī)實現(xiàn)頻率控制字的輸入和液晶顯示部分。FPGA與單片機(jī)通過串行輸入并行輸出的方式進(jìn)行通信。其總體設(shè)計框圖如圖1所示。

1.1 DDS產(chǎn)生原理

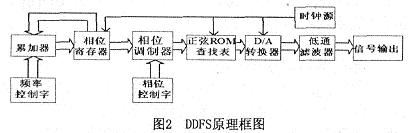

圖2是一個基本的DDFS結(jié)構(gòu)框圖。DDFS的優(yōu)點在于只用較少的器件就能實現(xiàn)任意正弦信號的產(chǎn)生,可運用到SoC系統(tǒng)實際的測試模塊中。以數(shù)控振蕩器的方式,產(chǎn)生頻率可控制的正弦波、方波、三角波,電路包括了基準(zhǔn)時鐘源、相位累加器、相位調(diào)制器、波形ROM查找表、D/A轉(zhuǎn)換器和低通濾波器等。

1.1.1 頻率部分

一個N位字長的二進(jìn)制加法器的一端和一個固定時鐘脈沖取樣的N位相位寄存器相連,另一個輸入端是外部輸入的控制字M。前相位寄存器中的值和當(dāng)前的M值相加,作為當(dāng)前相位寄存器的輸出。控制字M決定了相位增量,加法器不斷的對相位增量進(jìn)行線性累加。

時鐘信號都是總線數(shù)據(jù)傳輸?shù)耐筋l率,他們通常需要在時鐘信號的上升或下降沿進(jìn)行數(shù)據(jù)采樣,當(dāng)然,這些功能芯片時鐘芯片送給時鐘信號,還需要經(jīng)過倍頻或分頻運動老終滿足相應(yīng)總線數(shù)據(jù)傳輸?shù)男枰?/P>

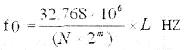

設(shè)基準(zhǔn)時鐘信號為fclk,分頻值為N,累加器位數(shù)為M,相位累加器步進(jìn)值為L,根據(jù)公式:

設(shè)頻率為20KHz,步進(jìn)為20Hz,因此累加器位數(shù)至少為10位(210=1024>20000/20)。為了保證在頻率下的波形在一個周期內(nèi)至少有32個點,因此累加器至少有l(wèi)O+5=15位。

取晶振頻率32.768MHz,可得

![]()

1.1.2 相位部分

相位寄存器的輸出通過相位調(diào)制器與相位控制字K相加,我們通過設(shè)置兩路信號的K值,使兩路信號有不同的相位偏移量,從而產(chǎn)生相位差△θ。設(shè)A路信號的控制字為K,B路信號的控制字為K’,考慮到FPGA的內(nèi)部資源,取512個采樣點,可得

![]()

通常我們只要改變控制字K就可以實現(xiàn)步進(jìn)調(diào)整。

1.2 DDS產(chǎn)生的軟件設(shè)計

1.2.1 FPGA軟件設(shè)計

FPGA負(fù)責(zé)接收由單片機(jī)送過來的頻率字與相位控制字,同時將波形在ROM中的數(shù)據(jù)送給DA轉(zhuǎn)換器進(jìn)行DA轉(zhuǎn)換,輸出正弦波、方波、三角波三種波形,通過調(diào)節(jié)DA轉(zhuǎn)換器的基準(zhǔn)電壓可調(diào)節(jié)輸出的正弦波、方波、三角波三種波形的幅度,利用按鍵可以設(shè)置一定范圍內(nèi)的頻率值和步進(jìn)值。

ROM是只讀內(nèi)存(Read-Only Memory)的簡稱,是一種只能讀出事先所存數(shù)據(jù)的固態(tài)半導(dǎo)體存儲器。其特性是一旦儲存資料就無法再將之改變或刪除。通常用在不需經(jīng)常變更資料的電子或電腦系統(tǒng)中,資料并且不會因為電源關(guān)閉而消失。

1.2.2 單片機(jī)軟件設(shè)計

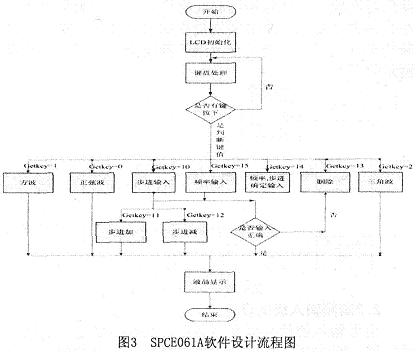

單片機(jī)軟件設(shè)計主要是負(fù)責(zé)接收鍵盤置入的頻率、步進(jìn)值、選擇波形并將其在液晶顯示屏中顯示和把各種控制信號和數(shù)據(jù)送到FPGA中。可設(shè)置任意頻率、任意步進(jìn)、波形切換等多種輸出方式,在此基礎(chǔ)上可擴(kuò)展為任意信號發(fā)生器,具體程序流程圖如圖3:

1.2.3 FPGA與單片機(jī)的通信

本系統(tǒng)設(shè)計中,F(xiàn)PGA與凌陽單片機(jī)采用串行輸入并行輸出的方式進(jìn)行通信。使用VHDL語言在EP2C20器件中利用D觸發(fā)器和移位寄存器接收凌陽單片機(jī)發(fā)送過來的頻率控制字和相位控制字,然后送入相位累加器。在FPGA與凌陽單片機(jī)通信中,單片機(jī)實行串行輸入,不斷地向FPGA送頻率控制字和相位控制字,送給FPGA實現(xiàn)相位累加。

2.等頻率計的實現(xiàn)

我們采用多周期同步測量法,即等測量法,通過對被測信號與閘門時間之間實現(xiàn)同步化,從而從根本上消除了在閘門時間內(nèi)對被測信號進(jìn)行計數(shù)時的 l量化誤差,使測量大大提高。

2.1 頻率測量總體設(shè)計與方案

隨著單片機(jī)功能集成化的發(fā)展,其應(yīng)用領(lǐng)域也逐漸地由傳統(tǒng)的控制,擴(kuò)展為控制處理數(shù)據(jù)處理以及數(shù)字信號處理,DSP( Digital Signal Processing)等領(lǐng)域。凌陽的16位單片機(jī)就是為適應(yīng)這種發(fā)展而設(shè)計的。

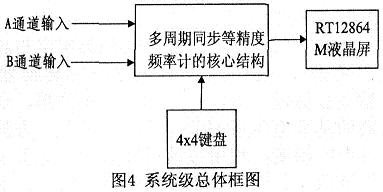

本系統(tǒng)主要是以凌陽單片機(jī)和FPGA為,多周期同步等測量頻率計的結(jié)構(gòu)用VHDL硬件描述語言對FPGA進(jìn)行編程,實現(xiàn)頻率、周期、脈沖寬度和占空比的測量。而單片機(jī)則作為控制部分實現(xiàn)了頻率計的控制、掃描和顯示,系統(tǒng)級框圖如下圖4:

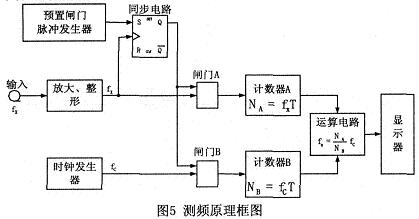

本設(shè)計頻率測量方法的主要測量原理如圖5所示,圖中預(yù)置門控信號GATE是由單片機(jī)發(fā)出,GATE的時間寬度對測頻影響較少,可以在較大的范圍內(nèi)選擇,根據(jù)理論計算GATE的時間寬度Tc可以大于42.94s,一般可在l0~0.1s間選擇,即在高頻段時,閘門時間較短;低頻時閘門時間較長。這樣閘門時問寬度Tc依據(jù)被測頻率的大小自動調(diào)整測頻,從而實現(xiàn)量程的自動轉(zhuǎn)換,擴(kuò)大了測頻的量程范圍;

2.2 測頻輸入級的設(shè)計

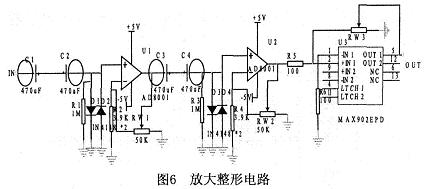

由于輸入的信號幅度不確定、波形不確定、邊沿不夠陡峭,F(xiàn)PGA只處理TTL電平的信號,因此我們必須對輸入信號進(jìn)行放大、整形處理。詳細(xì)設(shè)計的電路圖如圖6所示。

2.3 測頻的軟件設(shè)計

2.3.1 FPGA軟件設(shè)計

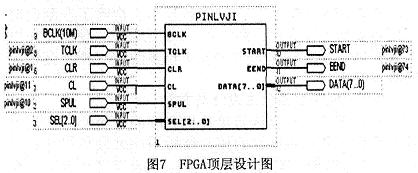

此頂層設(shè)計圖是通過VHDL硬件描述語言在QuartusII 5.1編程環(huán)境下實現(xiàn)對數(shù)字頻率計測量的設(shè)計圖,此設(shè)計與外部的凌陽16位單片機(jī)SPCE06lA以及輸入電路部分、顯示電路部分一起構(gòu)成完整的一個等數(shù)字頻率計的測量系統(tǒng)。

2.3.2 凌陽單片機(jī)SPCE061A軟件設(shè)計

SPCE06lA單片機(jī)的是對整個系統(tǒng)起到一個控制作用,軟件的設(shè)計主要是為了實現(xiàn)頻率計對頻率、周期、脈寬、占空比的測量的切換以及顯示,并利用凌陽自帶的語音播報功能實現(xiàn)頻率測量的實時播報。

3.系統(tǒng)的調(diào)試結(jié)果與分析

DDS信號發(fā)生器的調(diào)試結(jié)果:通過鍵盤輸入1HZ到4MHZ的正弦波、方波、三角波,設(shè)置三種波形的任意步進(jìn)大小,系統(tǒng)可以產(chǎn)生正弦波、方波、三角波這三種波形,其頻率分辨率可以達(dá)到O.Oll64153218269HZ,O.001%以上。等頻率計的調(diào)試結(jié)果:該系統(tǒng)具有能夠測量正弦波、方波、三角波三種波形的頻率、周期、脈寬和占空比的值,頻率的范圍可達(dá)到0.1HZ~30MHZ,達(dá)到0.001%以上,同時語音能實時播報待測信號參數(shù)。

4.結(jié)語

采用基于FPGA和凌陽16位單片機(jī)的DDS信號發(fā)生器設(shè)計,不僅控制方便、電路易實現(xiàn),而且穩(wěn)定性好、頻譜純凈、幅度恒定、失真小、分辨率高;等頻率計的設(shè)計,具有測量高、范圍寬;測量穩(wěn)定性好,不隨所測信號的變化而變化;使用凌陽16位單片機(jī)自帶的語音播報功能,不需外加語音芯片,能實時播報測得的頻率、周期、脈寬及占空比的大小。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- ARM技術(shù)架構(gòu)與應(yīng)用開發(fā)實踐指南2026/1/6 10:40:19

- 嵌入式實時操作系統(tǒng)(RTOS)選型與移植技術(shù)指南2025/12/31 10:42:31

- 工業(yè)嵌入式系統(tǒng):通信接口技術(shù)選型與抗干擾設(shè)計實踐2025/12/15 14:36:53

- 深入解析嵌入式 OPENAMP 框架:開啟異核通信新時代2025/7/22 16:27:29

- 一文快速了解OPENWRT基礎(chǔ)知識2025/7/14 16:59:04