一種無(wú)線視頻傳輸?shù)脑O(shè)計(jì)和實(shí)現(xiàn)

出處:現(xiàn)代電子技術(shù) 發(fā)布于:2011-09-05 14:34:57

無(wú)線通信技術(shù)和視頻壓縮技術(shù)的迅速發(fā)展,使得無(wú)線視頻傳輸成為人們研究的熱點(diǎn)。無(wú)線視頻傳輸具有數(shù)據(jù)量大,實(shí)時(shí)性要求高,無(wú)線信道資源有限的特點(diǎn)。無(wú)線視頻傳輸就是指不用布線(線纜)利用無(wú)線電波來(lái)傳輸視頻、聲音、數(shù)據(jù)等信號(hào)的監(jiān)控系統(tǒng)。無(wú)線圖像傳輸即視頻實(shí)時(shí)傳輸主要有兩個(gè)概念,一是移動(dòng)中傳輸,即移動(dòng)通信,二是寬帶傳輸,即寬帶通信。新一代的視頻壓縮標(biāo)準(zhǔn)H.264結(jié)合專用視頻DSF芯片可以滿足信源編碼的要求。而處理數(shù)據(jù)量大,速度快,運(yùn)算結(jié)構(gòu)相對(duì)簡(jiǎn)單的FPGA適用于信道編碼。基于以上考慮,設(shè)計(jì)了一個(gè)無(wú)線視頻傳輸系統(tǒng),并以發(fā)射端ADSP-BF537作為控制器,配置FPGA和進(jìn)行數(shù)據(jù)通信。

1 總體結(jié)構(gòu)實(shí)現(xiàn)方案

系統(tǒng)硬件的實(shí)現(xiàn)方案如下:

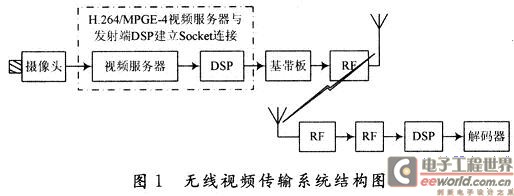

發(fā)送端由攝像機(jī)、專用視頻編碼芯片、控制模塊、基帶模塊、射頻模塊(RF)等部分組成。接收端由射頻接收模塊、控制模塊、基站模塊、專用視頻解碼芯片等部分組成。系統(tǒng)結(jié)構(gòu)如圖1所示。

視頻編碼部分使用基于DM642的H.264視頻編碼器。該芯片通過(guò)網(wǎng)口傳輸數(shù)據(jù),輸出的視頻流是H.264格式,輸出圖像的分辨率范圍為176×144~702×576,而且可以根據(jù)具體需要修改碼流和幀率。

控制模塊其主要作用是完成FPGA的配置、接口控制、通信鏈路的建立(視頻流數(shù)據(jù)的傳輸)。

FPGA完成整個(gè)基帶信號(hào)處理,包括信道編碼、OFDM調(diào)制、濾波等。

射頻模塊由發(fā)射單元、接收單元、頻率合成單元、外置15 W功放等四部分組成,采用差分I,Q信號(hào)調(diào)制、解調(diào),雙向傳輸。發(fā)射單元將I,Q差分輸入經(jīng)調(diào)制芯片調(diào)制成340 MHz的射頻信號(hào),經(jīng)功率控制、功放、隔離器送往環(huán)行器、天線;通過(guò)收發(fā)電平控制進(jìn)行發(fā)送和接收的切換;接收單元對(duì)接收信號(hào)進(jìn)行濾波、低噪聲放大器后送I,Q解調(diào)芯片解調(diào)出差分的I,Q信號(hào),并進(jìn)行RSSI檢測(cè)和AGC控制。工作模式采用半雙工模式;頻率合成單元為發(fā)射單元提供340 MHz本振信號(hào),為接收單元提供680 MHz本振信號(hào)。

2 控制模塊中DSP與FPGA數(shù)據(jù)通信

數(shù)字信號(hào)處理(Digital Signal Processing,簡(jiǎn)稱DSP)是一門(mén)涉及許多學(xué)科而又廣泛應(yīng)用于許多領(lǐng)域的新興學(xué)科。20世紀(jì)60年代以來(lái),隨著計(jì)算機(jī)和信息技術(shù)的飛速發(fā)展,數(shù)字信號(hào)處理技術(shù)應(yīng)運(yùn)而生并得到迅速的發(fā)展。數(shù)字信號(hào)處理是一種通過(guò)使用數(shù)學(xué)技巧執(zhí)行轉(zhuǎn)換或提取信息,來(lái)處理現(xiàn)實(shí)信號(hào)的方法,這些信號(hào)由數(shù)字序列表示。在過(guò)去的二十多年時(shí)間里,數(shù)字信號(hào)處理已經(jīng)在通信等領(lǐng)域得到極為廣泛的應(yīng)用。德州儀器、Freescale等半導(dǎo)體廠商在這一領(lǐng)域擁有很強(qiáng)的實(shí)力。

FPGA即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門(mén)電路數(shù)有限的缺點(diǎn)。FPGA一般來(lái)說(shuō)比ASIC(專用集成芯片)的速度要慢,無(wú)法完成復(fù)雜的設(shè)計(jì),而且消耗更多的電能。但是他們也有很多的優(yōu)點(diǎn)比如可以快速成品,可以被修改來(lái)改正程序中的錯(cuò)誤和更便宜的造價(jià)。

由于FPGA基于SRAM工藝,上電后數(shù)據(jù)會(huì)丟失。一般FPGA除了采用邊界掃描方式JTAG外,更多采用與FPGA相對(duì)應(yīng)PROM芯片靜態(tài)配置,這種配置方式由于PROM容量小,價(jià)格昂貴,易于燒壞等缺點(diǎn),在產(chǎn)品化之前一般不予采用,更可取的方法是采用控制器動(dòng)態(tài)配置FPGA,比如單片機(jī)、DSP。同時(shí),視頻服務(wù)器通過(guò)網(wǎng)口發(fā)送視頻數(shù)據(jù),需要一個(gè)控制部分前向網(wǎng)口接收視頻服務(wù)器的數(shù)據(jù),后向配置FPGA,發(fā)送視頻數(shù)據(jù)。基于以上考慮,整個(gè)系統(tǒng)中控制部分均由ADI公司的Blackfin系列DSP BF537完成,DSPBF537通過(guò)接口與視頻服務(wù)器和FPGA通信。

2.1 硬件平臺(tái)

ADSP與另外一個(gè)著名的德州儀器(TI: Texas Instrument)生產(chǎn)的芯片特點(diǎn)相比較,具有浮點(diǎn)運(yùn)算強(qiáng),SIMD(單指令多數(shù)據(jù))編程的優(yōu)勢(shì), 比較新的Blackfin系列比同別TI產(chǎn)品功耗低。缺點(diǎn)是ADSP不如TI的C語(yǔ)言編譯優(yōu)化好。TI已經(jīng)普及了C語(yǔ)言的編程,而AD芯片的性能發(fā)揮比較依賴程序員的編程水平。ADSP的Linkport數(shù)據(jù)傳輸能力強(qiáng)是一大特色,但是使用起來(lái)不夠穩(wěn)定,調(diào)試難度大。Blackfin處理器集成了一個(gè)由ADI公司和Intel公司聯(lián)合開(kāi)發(fā)的基于MSA(Micro Signal Architecture)的16/32位嵌入式處理器,支持32位RISC指令集,采用10級(jí)流水線,集成了兩個(gè)16位乘法加速器,內(nèi)核主頻可以達(dá)到600 MHz。ADSF-BF537總線有一個(gè)以DMA控制器為中心的高速自主數(shù)據(jù)通道。DMA總線可以在存儲(chǔ)器之間、存儲(chǔ)器和外部接口之間快速地傳遞數(shù)據(jù),并且可以和內(nèi)核并行操作。ADSP的集成開(kāi)發(fā)環(huán)境Visual DSP++中嵌入了實(shí)時(shí)操作系統(tǒng)內(nèi)核VDK,適合多任務(wù)多線程的嵌入式操作。

2.2 硬件系統(tǒng)架構(gòu)

DSP與視頻服務(wù)器采用輕量級(jí)TCP/IP(LwIP)交互數(shù)據(jù),這里不過(guò)多介紹。主要介紹DSP與FPGA連接。由于FPGA基于SRAM工藝,掉電后數(shù)據(jù)會(huì)丟失。采用的方法是將作用于FPGA的通信基帶算法文件存儲(chǔ)在DSP的FLASH中。一般調(diào)試時(shí),DSP及FPGA都需要從PC機(jī)通過(guò)JTAG口進(jìn)行程序的。但當(dāng)系統(tǒng)程序已經(jīng)調(diào)試完畢,當(dāng)需要到戶外進(jìn)行測(cè)試或作為產(chǎn)品使用時(shí),針對(duì)系統(tǒng)調(diào)試的方便性,采用DSP自啟動(dòng)及配置FPGA部分。

本設(shè)計(jì)中采用的DSP上電從16位FLASH啟動(dòng),啟動(dòng)程序采用Analog公司提供的燒寫(xiě)啟動(dòng)FLASH的程序。次上電時(shí),利用JTAG,結(jié)合ADSP自帶工具“FLASH Programmer”將寫(xiě)好的DSP程序燒入FLASH中。并且將FPGA的配置文件(.bit格式)讀到緩存,通過(guò)DSP燒寫(xiě)到FLASH的Bankl和Bank2中,把Bank0用來(lái)做DSP自啟動(dòng)。斷電復(fù)位后,啟動(dòng)過(guò)程如下:

(1)BF537從FLASH引導(dǎo)啟動(dòng),完成DSP板級(jí)初始化。

(2)FPGA的配置文件動(dòng)態(tài)加載到FPGA中。

(3)用DSP的GPIO端口對(duì)FPGA的時(shí)鐘和數(shù)據(jù)配置專用引腳進(jìn)行模擬時(shí)序,即完成對(duì)FPGA的動(dòng)態(tài)配置。

在啟動(dòng)過(guò)程完成后,DSP與視頻服務(wù)器進(jìn)行Sock-et連接,接收壓縮的視頻碼流,并送到FPGA進(jìn)行基帶部分的處理。DSP與FPGA的接口部分如圖2所示。

圖2中DSP通過(guò)自身的外部總線與FPGA相連,F(xiàn)PGA內(nèi)部實(shí)現(xiàn)了兩個(gè)2 KB的異步存儲(chǔ)器SRAM0,SRAM1,對(duì)存儲(chǔ)器的訪問(wèn)滿足DSP外部總線的時(shí)序要求。圖2中接口連線含義如表1所示。

對(duì)DSP而言,DSP通過(guò)外部總線連接到SRAM0和SRAM1,這就相當(dāng)于外擴(kuò)了兩個(gè)外部RAM,DSP可以自由地訪問(wèn)它們。圖2中的SRAM0,SRAM1分別用于DSP發(fā)送數(shù)據(jù)和接收數(shù)據(jù)。SRAM0和SRAM1本身是雙口RAM,可以供DSP和FPGA訪問(wèn),就是通過(guò)這種共享存儲(chǔ)器的方式完成數(shù)據(jù)交互。

2.3 軟件系統(tǒng)結(jié)構(gòu)

相關(guān)程序是用含有VDK(Visual DSP Kernel)的DSP軟件開(kāi)發(fā)工具Visual DSP開(kāi)發(fā)的。VDK是一種帶有API函數(shù)庫(kù)的實(shí)時(shí)操作系統(tǒng)內(nèi)核,它具有任務(wù)調(diào)度和任務(wù)管理功能,一共支持32個(gè)任務(wù)。VDK是整個(gè)軟件的基礎(chǔ),所有其他的程序都運(yùn)行在該Kernel上。程序流程圖如圖3所示。

上電或復(fù)位后,DSP自啟動(dòng)后VDK啟動(dòng)線程lwip_sysboot_threadtype開(kāi)始運(yùn)行。在線程lwip_sysboot_threadtype中進(jìn)行板級(jí)初始化和Lwip協(xié)議棧和網(wǎng)口初始化,其中板級(jí)初始化包括FPGA初始化,EBIU初始化,MDMA初始化,F(xiàn)LAG初始化。接下來(lái)創(chuàng)建下面幾個(gè)線程:

(1)數(shù)據(jù)傳輸:視頻數(shù)據(jù)傳輸。用于從編碼器獲取編碼后的視頻數(shù)據(jù)流,并存儲(chǔ)到緩沖區(qū)中。

(2)FPGA中斷:視頻數(shù)據(jù)發(fā)送中斷;MDMA中斷。

DSP首先通過(guò)Socket與視頻服務(wù)器連接,從視頻服務(wù)器獲取視頻數(shù)據(jù),并將數(shù)據(jù)緩存后按照特定的格式打包,等待FPGA觸發(fā)視頻數(shù)據(jù)發(fā)送中斷。中斷觸發(fā)后,DSP啟動(dòng)MDMA將一幀大小的數(shù)據(jù)發(fā)送給FPGA發(fā)送緩沖區(qū)。當(dāng)MDMA操作完成后,觸發(fā)MDMA中斷,將幀頭寫(xiě)入FPGA發(fā)送緩沖區(qū)的頭兩個(gè)字節(jié)。FPGA將接收的數(shù)據(jù)進(jìn)行基帶算法處理后再將數(shù)據(jù)發(fā)送給射頻部分,之后FPGA再觸發(fā)視頻數(shù)據(jù)發(fā)送中斷,告訴DSP可以下一幀的發(fā)送,于是又啟動(dòng)MDMA,如此循環(huán)。

3 實(shí)驗(yàn)結(jié)果和分析

對(duì)系統(tǒng)在不同的信噪比的環(huán)境中傳輸?shù)恼`碼率進(jìn)行了測(cè)試。測(cè)試方法如下:將發(fā)射機(jī)的輸出端口通過(guò)數(shù)據(jù)排線與邏輯分析儀相連,邏輯分析儀將采集到的一幀發(fā)射信號(hào)送到PC中用Matlab軟件對(duì)其加上噪聲,得到信噪比固定的信號(hào)。將這個(gè)信號(hào)導(dǎo)人信號(hào)源中進(jìn)行不間斷循環(huán)發(fā)送給接收端的輸入端口。接收機(jī)接收信號(hào)進(jìn)行解調(diào)并將解調(diào)出的數(shù)據(jù)傳給PC以統(tǒng)計(jì)誤碼率。測(cè)試結(jié)果如表2所示。

4 結(jié) 語(yǔ)

隨著實(shí)驗(yàn)環(huán)節(jié)在BF537產(chǎn)品開(kāi)發(fā)過(guò)程中所占時(shí)間和開(kāi)銷的迅速增加,Altera和Xilinx在其大容量FPGA芯片產(chǎn)品中,都集成了特定類型的CPU作為系統(tǒng)處理器,但它們都受到特定FPGA器件的限制。因此利用ADSP內(nèi)嵌的強(qiáng)大Blackfin處理器和豐富的DSP外設(shè),可以有效地提高驗(yàn)證的效率和功能的完整性。本文的總線接口模塊的設(shè)計(jì)對(duì)具有不同讀寫(xiě)時(shí)序的驗(yàn)證板的正常工作起著重要的作用,BF537原型的搭建必然要求本模塊能真實(shí)反映實(shí)際AHB總線的動(dòng)作,這樣對(duì)于保證各個(gè)功能模塊的完整性和實(shí)時(shí)工作將起很大的作用。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫(kù)電子市場(chǎng)網(wǎng)”的所有作品,版權(quán)均屬于維庫(kù)電子市場(chǎng)網(wǎng),轉(zhuǎn)載請(qǐng)必須注明維庫(kù)電子市場(chǎng)網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問(wèn)題,請(qǐng)?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- 掌握 DSP:原理剖析與應(yīng)用實(shí)踐2025/5/8 14:03:24

- 模糊邏輯在 DSP 上實(shí)時(shí)執(zhí)行2023/7/25 17:13:30

- 多速率DSP及其在數(shù)模轉(zhuǎn)換中的應(yīng)用2023/6/12 15:28:52

- 使用 DSP 加速 CORDIC 算法2023/3/29 15:46:30

- 高速DSP系統(tǒng)的信號(hào)完整性2022/9/26 16:45:38

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號(hào)完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號(hào)鏈中的濾波與功耗管理