確保PCB設(shè)計(jì)成功的關(guān)鍵幾步!

出處:維庫電子市場(chǎng)網(wǎng) 發(fā)布于:2016-10-21 15:05:34

為了把產(chǎn)品快速可靠地推向市場(chǎng),利用設(shè)計(jì)工具實(shí)現(xiàn)設(shè)計(jì)流程自動(dòng)化就顯得十分必要,但如何才能確保設(shè)計(jì)獲得成功呢?為了地提高設(shè)計(jì)效率和產(chǎn)品質(zhì)量,應(yīng)當(dāng)關(guān)注哪些細(xì)節(jié)?設(shè)計(jì)工具顯然應(yīng)該直觀易用且足夠強(qiáng)大,以便克服復(fù)雜的設(shè)計(jì)挑戰(zhàn),但還有哪些事項(xiàng)值得注意?

步:不要停留于基本原理圖輸入

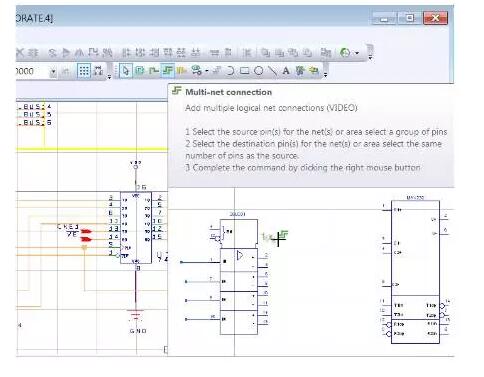

原理圖輸入對(duì)于生成設(shè)計(jì)的邏輯連接而言至關(guān)重要,其必須準(zhǔn)確無誤、簡(jiǎn)單易用且與布局集成為一體才能確保設(shè)計(jì)成功。

簡(jiǎn)單地輸入原理圖并將其傳送到布局還不夠。為了創(chuàng)建符合預(yù)期的高質(zhì)量設(shè)計(jì),需要確保使用元件,并且可以執(zhí)行仿真分析,從而保證設(shè)計(jì)在交付制造時(shí)不會(huì)出問題。

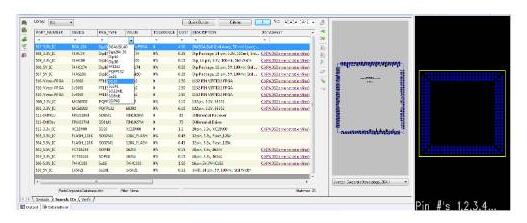

管理是設(shè)計(jì)流程的重要組成部分。為了快速選擇元件并將其放置在設(shè)計(jì)中,器件的簡(jiǎn)易創(chuàng)建和輕松管理就顯得十分必要了。

PADS 允許您在一個(gè)庫中維護(hù)所有設(shè)計(jì)任務(wù),并可實(shí)時(shí)更新該庫,以便于使用并確保設(shè)計(jì)開發(fā)的性。您可以通過單個(gè)電子表格來訪問所有元器件信息,而無需擔(dān)心數(shù)據(jù)冗余、多個(gè)庫或耗時(shí)費(fèi)力的工具開銷。

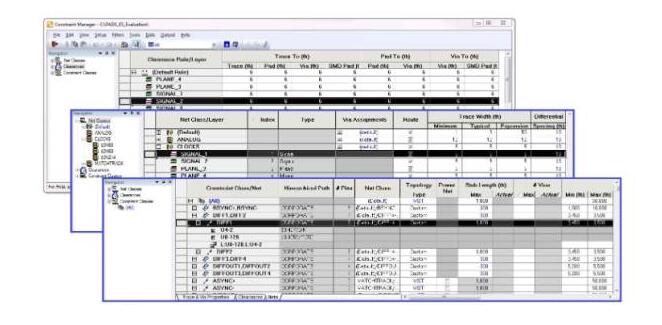

當(dāng)今的關(guān)鍵高速設(shè)計(jì)異常復(fù)雜,如果沒有有效的手段來管理約束規(guī)則,則對(duì)走線、拓?fù)浜托盘?hào)延遲等方面的設(shè)計(jì)、約束和管理將會(huì)變得異常困難。為了在次迭代中就構(gòu)建出成功的產(chǎn)品,必須在設(shè)計(jì)流程的早期設(shè)置約束規(guī)則,以便設(shè)計(jì)達(dá)到要求的目標(biāo)。良好的約束規(guī)則管理可防止您使用價(jià)格高昂或無法采購到的元件,并且終確保電路板符合性能和制造要求。

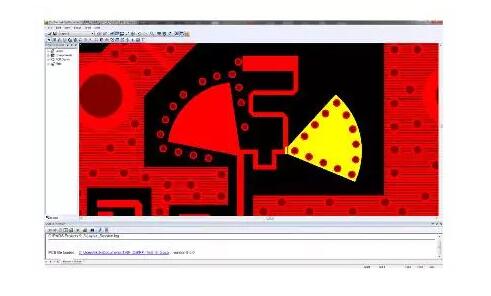

近年來,PCB 布局設(shè)計(jì)的復(fù)雜度顯著高于以前。為了制造更小型、更便攜的電子裝置,設(shè)計(jì)的密度不得不提高。此外,工作頻率也被提高,這就要求設(shè)計(jì)人員評(píng)估以前可能遭到忽略的電氣特性以確保設(shè)計(jì)可用。為了跟上日益復(fù)雜的步伐,設(shè)計(jì)人員必須具備更廣泛的能力,以便定義規(guī)則集,創(chuàng)建獨(dú)特的射頻形狀并實(shí)施校正結(jié)構(gòu)來改善設(shè)計(jì)的總體性能。

布局過程中,智能布局工具有助于創(chuàng)建高效的布置和布線策略。精密布置可減少設(shè)計(jì)后期的違規(guī)情況,讓您能夠能在少犯錯(cuò)誤的情況下更快速地完成項(xiàng)目。

另一個(gè)挑戰(zhàn)是現(xiàn)代 PCB 要維護(hù)成千上萬的網(wǎng)絡(luò),這可能會(huì)為在設(shè)計(jì)中的關(guān)鍵區(qū)域布線帶來困難。避免這個(gè)問題的辦法是將網(wǎng)絡(luò)線分成組,以便創(chuàng)建有效的布線策略。創(chuàng)建規(guī)劃組后,便可標(biāo)記并過濾網(wǎng)絡(luò)組,以突出顯示需要布線的關(guān)鍵網(wǎng)絡(luò)。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場(chǎng)網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場(chǎng)網(wǎng),轉(zhuǎn)載請(qǐng)必須注明維庫電子市場(chǎng)網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請(qǐng)?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- 高速PCB阻抗控制核心實(shí)操規(guī)范2026/4/17 11:39:12

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范2026/4/15 14:39:47

- 多層PCB疊層設(shè)計(jì)核心實(shí)操規(guī)范2026/4/14 16:02:09

- PCB焊盤與過孔設(shè)計(jì)核心實(shí)操規(guī)范(含可焊性與可靠性保障)2026/4/13 16:14:19

- 高速PCB信號(hào)完整性(SI)設(shè)計(jì)核心實(shí)操規(guī)范2026/4/10 11:24:24

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號(hào)完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號(hào)鏈中的濾波與功耗管理