摩爾定律還能走多遠(yuǎn)?—— CPU 的內(nèi)存瓶頸

出處:維庫電子市場網(wǎng) 發(fā)布于:2016-08-02 14:10:32

1995年的奔騰芯片,時(shí)鐘頻率達(dá)到了 100 兆赫, 是 1980年的二十倍還多。

而到了 2002年, 英特爾新型奔騰芯片時(shí)鐘頻率次突破 3000 兆赫 (3 GHz)。

限制時(shí)鐘頻率的個(gè)主要物理約束條件是: 信號(hào)在晶體管之間傳輸?shù)倪t滯。 這也是為什么晶體管密度越大,時(shí)鐘頻率可以越高。

2002年之后, CPU 時(shí)鐘頻率增加遇到了第二個(gè)技術(shù)瓶頸: 能量消耗。

簡單說, CPU的能量消耗和時(shí)鐘頻率的三次方近似成正比, 在 3 Ghz 之后, 頻率的繼續(xù)提高會(huì)使芯片過熱而面臨被燒毀的風(fēng)險(xiǎn)。

實(shí)際上, 2002 年之后, 英特爾CPU 的時(shí)鐘頻率大多一直在 2 GHz - 4 GHz 之間, 十四年來沒有本質(zhì)提高。

這時(shí)候,有用的思路,是尋找新的維度,去進(jìn)攻解決問題。

如果說, CPU的時(shí)鐘速度好比人腦的計(jì)算速度, 那么 CPU 的內(nèi)存讀取速度就好比人獲取信息的速度。 這是提升 CPU 性能的個(gè)不同的維度。

有過基本工作或者研究經(jīng)驗(yàn)的人,都會(huì)有這樣的體會(huì):

大多數(shù)時(shí)候,限制工作效率的瓶頸是: 查資料,找東西。

找不到就只能干著急。

二十年前的科研者,查資料要去圖書館,小圖書館沒有資料就要去更大的圖書館,沒有計(jì)算機(jī)檢索之前需要一張張翻卡片查。 查找資料的時(shí)間,動(dòng)輒就是幾個(gè)小時(shí)甚至更多,超過了真正研究分析的時(shí)間。 這和今天,十秒鐘內(nèi)就可以在互聯(lián)網(wǎng)上,精準(zhǔn)搜索和世界上大部分論文資料,完全不可同日而語。

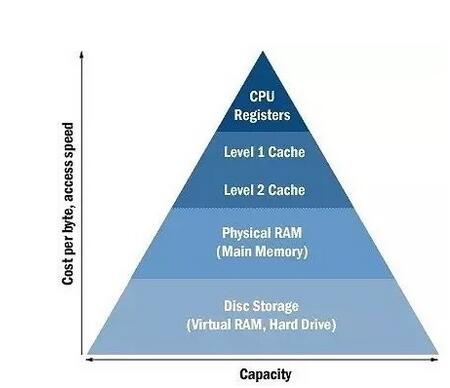

電腦的內(nèi)存架構(gòu),實(shí)際上要細(xì)分為 Register (寄存器), Cache (高速緩存), Memory(內(nèi)存), Disk (硬盤)。 而緩存又可以細(xì)分為緩存 (Level 1 Cache), 二級(jí)緩存, 三級(jí)緩存, 甚至四級(jí)緩存。

緩存, 好比桌面上的書, 信息量多一些, 伸一下手可以拿到;

二級(jí)緩存, 好比抽屜里的書,打開抽屜后仍然很快可以拿到;

內(nèi)存,好比書架上的書,要站起來去查找;

硬盤,就是圖書館的資料,需要花幾個(gè)小時(shí)到外面跑一趟才可以查到了。

研究者,如果無法迅速獲取需要的資料,天天要往圖書館跑,即使牛頓/愛因斯坦再世, 聰明的腦瓜也只能像高速的 CPU 一樣, 無效地空轉(zhuǎn), 痛苦地在來去圖書館的道路上等待。

以 Intel 的 i7-4770 CPU 為例,其時(shí)鐘頻率 3.4 GHz. 和二級(jí)緩存,讀取數(shù)據(jù)的延遲一般在 5 - 12個(gè)時(shí)鐘周期,相當(dāng)于約 2-4 納秒。如果要到內(nèi)存讀取數(shù)據(jù),遲滯則約 70 納秒,等價(jià)于200多個(gè)時(shí)鐘周期。如果內(nèi)存找不到,不幸地要去硬盤搜索,延遲超過 4 毫秒 (等價(jià)于四百萬納秒),再快的 CPU 時(shí)鐘頻率, 此時(shí)也然并卵矣。

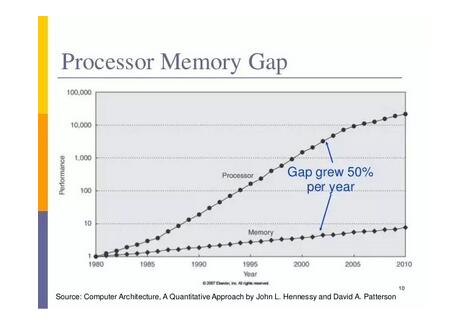

摩爾定律的發(fā)展,對(duì)于 CPU 的時(shí)鐘速度,和普通內(nèi)存 (DRAM) 的讀取延遲上,進(jìn)步速度是不一樣的。其差距每年以 50%的速度增長。

真正的芯片上的內(nèi)置的緩存,早是在1989年的 486處理器上出現(xiàn),當(dāng)時(shí)容量只有 8 KB, 到九十年代容量提高到 16 KB.

緩存容量過大,會(huì)影響搜尋速度,所以又出現(xiàn)了二級(jí), 三級(jí)緩存。 這里有很多微妙的設(shè)計(jì)細(xì)節(jié),此處不表。

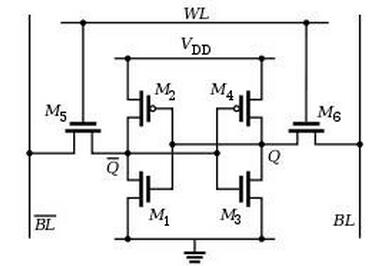

緩存, 本質(zhì)上就是以 SRAM (靜態(tài)隨機(jī)存儲(chǔ)器)為基礎(chǔ)的內(nèi)存。 而SRAM, 本質(zhì)上就是六個(gè)晶體管結(jié)構(gòu)組成的邏輯單元, 如下圖。

以 2015年九月英特爾出品的 14 納米 i7-6560U 處理器為例, 它有兩個(gè)內(nèi)核 (core), 每個(gè)內(nèi)核有 64 KB 的緩存, 256 KB 的二級(jí)緩存, 并共享一個(gè) 4 MB的三級(jí)緩存。

用于緩存的晶體管占整個(gè)CPU 芯片上的晶體管的比例,也從 486時(shí)代的 40%左右,到今天許多CPU上接近 90%. (數(shù)據(jù)出處來自威斯康辛大學(xué) Doug Burger 的論文, “Syetem-level Implication of Processor Memory Integration” )

換句話說,計(jì)算的管理,將近90%的內(nèi)涵, 實(shí)際上是對(duì)內(nèi)存記憶的管理。

不管在什么行業(yè),如果做到了高效地搜尋和存儲(chǔ)海量的數(shù)據(jù), 你可能就已經(jīng)成功了90%.

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請(qǐng)必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請(qǐng)?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- 主流存儲(chǔ)技術(shù)核心特性與場景化應(yīng)用概述2026/1/13 11:12:42

- 主流存儲(chǔ)技術(shù)特性與場景化選型指南2026/1/7 10:07:41

- MES系統(tǒng)現(xiàn)場部署與數(shù)據(jù)對(duì)接實(shí)操指南2025/12/29 11:09:41

- eMMC 屬于閃存還是內(nèi)存?從定義到應(yīng)用講透核心區(qū)別2025/9/15 15:24:16

- ddr4和ddr5內(nèi)存接口一樣嗎?全景解析2025/9/8 17:22:03

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號(hào)完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號(hào)鏈中的濾波與功耗管理