如何正確使用PCB的分層和堆疊?

出處:維庫電子市場(chǎng)網(wǎng) 發(fā)布于:2017-04-07 14:47:54

1.概述

多層印制板為了有更好的電磁兼容性設(shè)計(jì)。使得印制板在正常工作時(shí)能滿足電磁兼容和敏感度標(biāo)準(zhǔn)。正確的堆疊有助于屏蔽和抑制EMI。

2.多層印制板設(shè)計(jì)基礎(chǔ)。

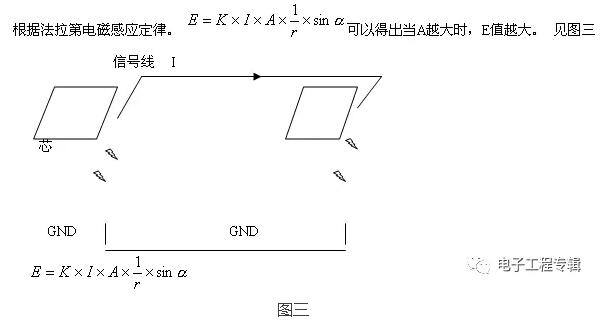

多層印制板的電磁兼容分析可以基于克希霍夫定律和法拉第電磁感應(yīng)定律。

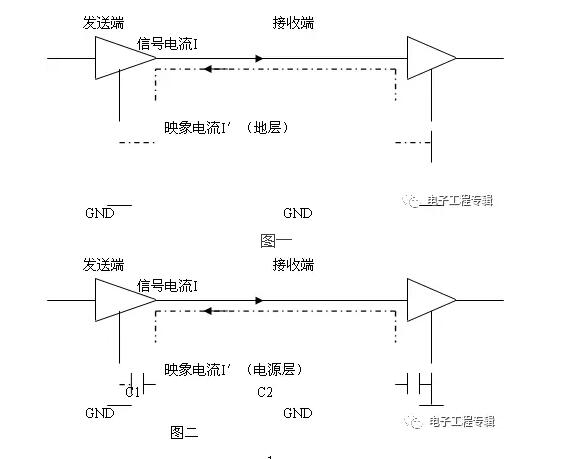

根據(jù)克希霍夫定律,任何時(shí)域信號(hào)由源到負(fù)載的傳輸都必須有一個(gè)阻抗的路徑。見圖一。圖中I=I′,大小相等,方向相反。圖中I我們稱為信號(hào)電流,I′稱為映象電流,而I′所在的層我們稱為映象平面層。如果信號(hào)電流下方是電源層(POWER),此時(shí)的映象電流回路是通過電容耦合所達(dá)到的。見圖二。

根據(jù)以上兩個(gè)定律,我們得出在多層印制板分層及堆疊中應(yīng)遵循以下基本原則:

① 電源平面應(yīng)盡量靠近接地平面,并應(yīng)在接地平面之下。

② 布線層應(yīng)安排與映象平面層相鄰。

③ 電源與地層阻抗。

④ 在中間層形成帶狀線,表面形成微帶線。兩者特性不同。

⑤ 重要信號(hào)線應(yīng)緊臨地層。

3. PCB板的堆疊與分層

① 二層板。

此板僅能用于低速設(shè)計(jì)。EMC比較差。

② 四層板。

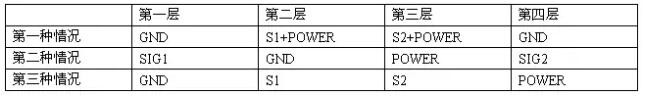

由以下幾種疊層順序。下面分別把各種不同的疊層優(yōu)劣作說明。

表一

注:S1 信號(hào)布線一層,S2 信號(hào)布線二層;GND 地層;POWER 電源層

種情況,應(yīng)當(dāng)是四層板中的一種情況。因?yàn)橥鈱邮堑貙樱瑢?duì)EMI有屏蔽作用,同時(shí)電源層同地層也可靠得很近,使得電源內(nèi)阻較小,取得效果。但種情況不能用于當(dāng)本板密度比較大的情況。因?yàn)檫@樣一來,就不能保證層地的完整性,這樣第二層信號(hào)會(huì)變得更差。另外,此種結(jié)構(gòu)也不能用于全板功耗比較大的情況。

表中的第二種情況,是我們平時(shí)常用的一種方式。從板的結(jié)構(gòu)上,也不適用于高速數(shù)字電路設(shè)計(jì)。因?yàn)樵谶@種結(jié)構(gòu)中,不易保持低電源阻抗。以一個(gè)板2毫米為例:要求Z0=50ohm. 以線寬為8mil.銅箔厚為35цm。這樣信號(hào)一層與地層中間是0.14mm。而地層與電源層為1.58mm。這樣就大大的增加了電源的內(nèi)阻。在此種結(jié)構(gòu)中,由于輻射是向空間的,需加屏蔽板,才能減少EMI。

表中第三種情況,S1層上信號(hào)線質(zhì)量。S2次之。對(duì)EMI有屏蔽作用。但電源阻抗較大。此板能用于全板功耗大而該板是干擾源或者說緊鄰著干擾源的情況下。

③ 六層板

表二

A種情況,是常見的方式之一,S1是比較好的布線層。S2次之。但電源平面阻抗較差。布線時(shí)應(yīng)注意S2對(duì)S3層的影響。

B種情況,S2層為好的布線層,S3層次之。電源平面阻抗較好。

C種情況,這種情況是六層板中的情況,S1,S2,S3都是好的布線層。電源平面阻抗較好。美中不足的是布線層同前兩種情況少了一層。

D種情況,在六層板中,性能雖優(yōu)于前三種,但布線層少于前兩種。此種情況多在背板中使用。

④ 八層板

表三

八層板,如果要有6個(gè)信號(hào)層,以A種情況為。但此種排列不宜用于高速數(shù)字電路設(shè)計(jì)。如果是5個(gè)信號(hào)層,以C種情況為。在這種情況中,S1,S2,S3都是比較好的布線層。同時(shí)電源平面阻抗也比較低。如果是4個(gè)信號(hào)層,以表三中B種情況為。每個(gè)信號(hào)層都是良好布線層。在這幾種情況中,相鄰信號(hào)層應(yīng)布線。

⑤ 十層板

表四

十層板如果有6個(gè)信號(hào)層,有A,B,C三種疊層順序。A種情況為,C種次之,B種情況差。其它沒有列出的情況,比這幾種情況更差。在A種情況中,S1,S6是比較好的布線層。S2,S3,S5次之。這中間要特別指出的是,A同C,A種情況之所以好于C種情況,主要原因是因?yàn)樵贑種情況中,GND層同POWER層的距離是由S5同GND層距離決定的。這樣就不一定能保證GND層同POWER層的電源平面阻抗。D種情況應(yīng)當(dāng)說是十層板中綜合性能的疊層順序。每個(gè)信號(hào)層都是優(yōu)良的布線層。E、F多用于背板。其中F種情況對(duì)EMC的屏蔽作用要好于E。不足之處是在于兩信號(hào)層相接,在布線上要注意。

總之,PCB的分層及疊層是一個(gè)比較復(fù)雜的事情。有多方面的因素要考慮。但我們應(yīng)當(dāng)記住我們要完成的功能,需要那些關(guān)鍵因素。這樣才能找到一個(gè)符合我們要求的印制板分層及疊層順。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場(chǎng)網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場(chǎng)網(wǎng),轉(zhuǎn)載請(qǐng)必須注明維庫電子市場(chǎng)網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請(qǐng)?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- 高速PCB阻抗控制核心實(shí)操規(guī)范2026/4/17 11:39:12

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范2026/4/15 14:39:47

- 多層PCB疊層設(shè)計(jì)核心實(shí)操規(guī)范2026/4/14 16:02:09

- PCB焊盤與過孔設(shè)計(jì)核心實(shí)操規(guī)范(含可焊性與可靠性保障)2026/4/13 16:14:19

- 高速PCB信號(hào)完整性(SI)設(shè)計(jì)核心實(shí)操規(guī)范2026/4/10 11:24:24

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號(hào)完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號(hào)鏈中的濾波與功耗管理