9大硬件工程師談高速PCB信號(hào)走線規(guī)則

出處:維庫(kù)電子市場(chǎng)網(wǎng) 發(fā)布于:2017-08-25 16:37:49

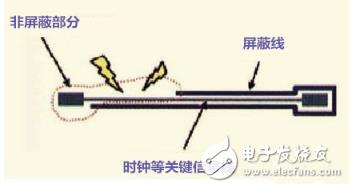

規(guī)則一:高速信號(hào)走線屏蔽規(guī)則

在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號(hào)線,走線需要進(jìn)行屏蔽處理,如果沒(méi)有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

圖1 高速信號(hào)線

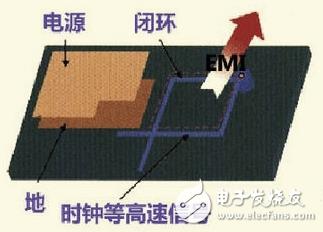

規(guī)則二:高速信號(hào)的走線閉環(huán)規(guī)則

由于PCB板的密度越來(lái)越高,很多PCB LAYOUT工程師在走線的過(guò)程中,很容易出現(xiàn)一種失誤,即時(shí)鐘信號(hào)等高速信號(hào)網(wǎng)絡(luò),在多層的PCB走線的時(shí)候產(chǎn)生了閉環(huán)的結(jié)果,這樣的閉環(huán)結(jié)果將產(chǎn)生環(huán)形天線,增加EMI的輻射強(qiáng)度。

圖2 閉環(huán)規(guī)則

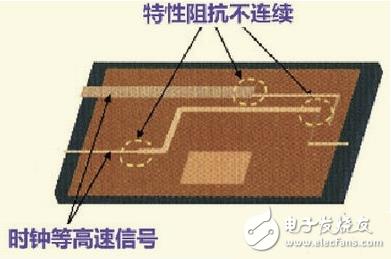

規(guī)則三:高速信號(hào)的走線開(kāi)環(huán)規(guī)則

規(guī)則二提到高速信號(hào)的閉環(huán)會(huì)造成EMI輻射,然而開(kāi)環(huán)同樣會(huì)造成EMI輻射。

時(shí)鐘信號(hào)等高速信號(hào)網(wǎng)絡(luò),在多層的PCB走線的時(shí)候一旦產(chǎn)生了開(kāi)環(huán)的結(jié)果,將產(chǎn)生線形天線,增加EMI的輻射強(qiáng)度。

圖3 開(kāi)環(huán)規(guī)則

規(guī)則四:高速信號(hào)的特性阻抗連續(xù)規(guī)則

高速信號(hào),在層與層之間切換的時(shí)候必須保證特性阻抗的連續(xù),否則會(huì)增加EMI的輻射。也就是說(shuō),同層的布線的寬度必須連續(xù),不同層的走線阻抗必須連續(xù)。

圖4 特性阻抗連續(xù)規(guī)則

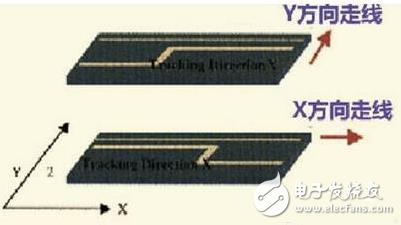

規(guī)則五:高速PCB設(shè)計(jì)的布線方向規(guī)則

相鄰兩層間的走線必須遵循垂直走線的原則,否則會(huì)造成線間的串?dāng)_,增加EMI輻射。

簡(jiǎn)而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直的布線可以抑制線間的串?dāng)_。

圖5 布線方向

規(guī)則六:高速PCB設(shè)計(jì)中的拓?fù)浣Y(jié)構(gòu)規(guī)則

在高速PCB設(shè)計(jì)中,線路板特性阻抗的控制和多負(fù)載情況下的拓?fù)浣Y(jié)構(gòu)的設(shè)計(jì),直接決定著產(chǎn)品的成功還是失敗。

圖示為菊花鏈?zhǔn)酵負(fù)浣Y(jié)構(gòu),一般用于幾Mhz的情況下為益。高速PCB設(shè)計(jì)中建議使用后端的星形對(duì)稱結(jié)構(gòu)。

圖6 拓?fù)浣Y(jié)構(gòu)

規(guī)則七:走線長(zhǎng)度的諧振規(guī)則

檢查信號(hào)線的長(zhǎng)度和信號(hào)的頻率是否構(gòu)成諧振,即當(dāng)布線長(zhǎng)度為信號(hào)波長(zhǎng)1/4的時(shí)候的整數(shù)倍時(shí),此布線將產(chǎn)生諧振,而諧振就會(huì)輻射電磁波,產(chǎn)生干擾。

圖7 諧振規(guī)則

規(guī)則八:回流路徑規(guī)則

所有的高速信號(hào)必須有良好的回流路徑。盡可能地保證時(shí)鐘等高速信號(hào)的回流路徑。否則會(huì)極大的增加輻射,并且輻射的大小和信號(hào)路徑和回流路徑所包圍的面積成正比。

圖8 回流路徑

規(guī)則九:器件的退耦電容擺放規(guī)則

退耦電容的擺放的位置非常的重要。擺放不合理根本起不到退耦的效果。其原則是:靠近電源的管腳,并且電容的電源走線和地線所包圍的面積。

圖9 退耦電容

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫(kù)電子市場(chǎng)網(wǎng)”的所有作品,版權(quán)均屬于維庫(kù)電子市場(chǎng)網(wǎng),轉(zhuǎn)載請(qǐng)必須注明維庫(kù)電子市場(chǎng)網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問(wèn)題,請(qǐng)?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- 高速PCB阻抗控制核心實(shí)操規(guī)范2026/4/17 11:39:12

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范2026/4/15 14:39:47

- 多層PCB疊層設(shè)計(jì)核心實(shí)操規(guī)范2026/4/14 16:02:09

- PCB焊盤(pán)與過(guò)孔設(shè)計(jì)核心實(shí)操規(guī)范(含可焊性與可靠性保障)2026/4/13 16:14:19

- 高速PCB信號(hào)完整性(SI)設(shè)計(jì)核心實(shí)操規(guī)范2026/4/10 11:24:24

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號(hào)完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號(hào)鏈中的濾波與功耗管理