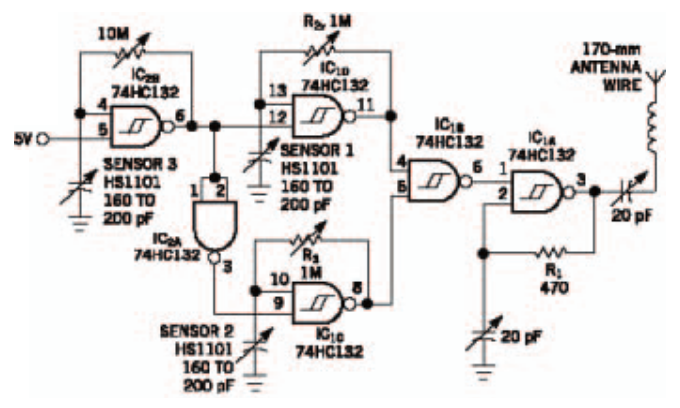

雙邊沿檢測電路圖

出處:rin 發(fā)布于:2009-10-30 00:00:00 | 8618 次閱讀

圖1是由異或門組成的雙邊沿(上升和下降)檢測電路。異或門是在門輸人端子邏輯不一致時輸出“H”電平,如采用RC電路產生延遲時間,則在上升、下降時檢測出邊沿,得到微分脈沖輸出。

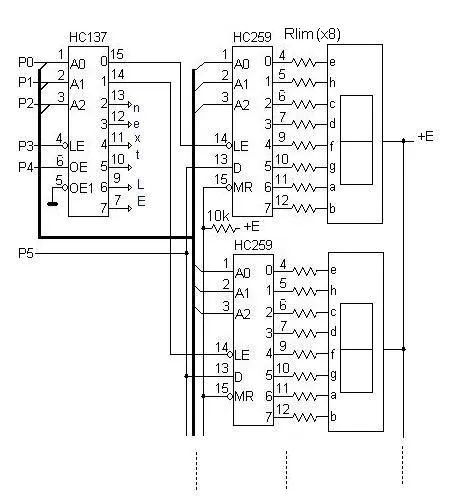

圖2是電容C的端子電壓波形。74HC86的閾值電壓VTH為VDD/2,在此處放人標記線。從對應輸人上升開始,到達到C端子電壓VTH之前的時間和從輸人下降開始,到達到C端子電壓yTH之前的時間都可得到輸出脈沖。

從這種雙邊沿檢測電路輸出波形的時間軸看,頻率變?yōu)檩斎祟l率的2倍,因此,此電路也可作為2倍頻電路使用。

圖1 上升/下降雙邊沿檢測電路

圖2上升沿檢測電路的輸人輸出波形(R=10kΩ,C=1000pF,ZV/div.,10μs/div)

上一篇:使用NAND門的邊沿檢測電路圖

下一篇:晶閘管采用萬用表檢測電路圖

版權與免責聲明

凡本網注明“出處:維庫電子市場網”的所有作品,版權均屬于維庫電子市場網,轉載請必須注明維庫電子市場網,http://hbjingang.com,違反者本網將追究相關法律責任。

本網轉載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網贊同其觀點或證實其內容的真實性,不承擔此類作品侵權行為的直接責任及連帶責任。其他媒體、網站或個人從本網轉載時,必須保留本網注明的作品出處,并自負版權等法律責任。

如涉及作品內容、版權等問題,請在作品發(fā)表之日起一周內與本網聯(lián)系,否則視為放棄相關權利。