轉(zhuǎn)換器時(shí)鐘技術(shù)發(fā)展成高速數(shù)據(jù)時(shí)鐘

出處:awey 發(fā)布于:2011-08-18 15:25:29 | 2417 次閱讀

轉(zhuǎn)換器時(shí)鐘

基站收發(fā)器、寬帶調(diào)制解調(diào)器和高端儀器儀表通常需要具有高動(dòng)態(tài)范圍和高采樣率的ADC和/或DAC.高動(dòng)態(tài)范圍是為了將信號(hào)解析到所需的。高采樣率則是處理高帶寬信號(hào)所必需的。無論是無線電系統(tǒng)、調(diào)制解調(diào)器或者是測量儀器,對轉(zhuǎn)換器的要求將取決于整個(gè)系統(tǒng)的規(guī)格參數(shù)和架構(gòu)。該轉(zhuǎn)換器的采樣時(shí)鐘的頻譜純度往往會(huì)對實(shí)際達(dá)到的性能產(chǎn)生重大影響。

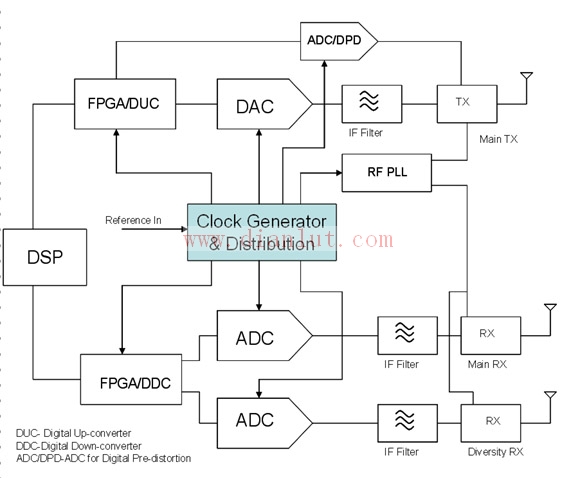

一個(gè)無線收發(fā)器電路的例子如圖1所示。除了為ADC和DAC提供時(shí)鐘,時(shí)鐘發(fā)生器還負(fù)責(zé)將時(shí)鐘信號(hào)分配到收發(fā)器卡上的其他幾個(gè)電路模塊。接下來我們將集中討論時(shí)鐘抖動(dòng)和相位噪聲對ADC性能的影響。

圖1:收發(fā)器系統(tǒng)框圖

無線電接收器中ADC的一個(gè)關(guān)鍵指標(biāo)是信噪比(SNR),它將影響到ADC在給定幅度范圍內(nèi)能夠達(dá)到的信號(hào)采樣。理想情況下,ADC應(yīng)該能夠以很高的分辨率將非常小的模擬輸入信號(hào)轉(zhuǎn)換成的數(shù)字信號(hào)。按照無線電術(shù)語,ADC的SNR將決定最小可檢測信號(hào)(MDS)。

N位轉(zhuǎn)換器基于量化噪聲的理論SNR等于:

SNR = 6.02(N) + 1.8 db

因此,對于一個(gè)14位轉(zhuǎn)換器,其可以實(shí)現(xiàn)的SNR大約為86db.

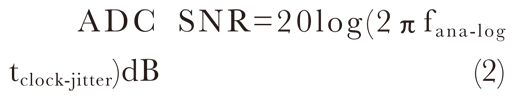

在IF采樣架構(gòu)中,如圖1所示框圖,對時(shí)鐘抖動(dòng)的要求可以說非常嚴(yán)格。事實(shí)上,提供給ADC的時(shí)鐘的質(zhì)量常常是系統(tǒng)SNR性能的一個(gè)限制因素。這可以通過以下公式來理解。

這個(gè)公式定義了采樣時(shí)鐘的寬帶抖動(dòng)與ADC在某一給定模擬輸入頻率抖動(dòng)情況下可以達(dá)到的SNR之間的關(guān)系。舉例來說,如果采樣時(shí)鐘的寬帶抖動(dòng)為275fs ,對170MHz的中頻信號(hào)采樣時(shí),SNR基本上不會(huì)高于70.65db.

實(shí)際上,ADC內(nèi)的其他噪聲機(jī)制通常會(huì)將SNR值限制在低于理論水平或量化噪聲(公式1) .這一內(nèi)部噪聲是由于模擬信號(hào)路徑和采樣時(shí)鐘路徑中的器件熱噪聲而引起的。采樣時(shí)鐘路徑中的器件噪聲有效地轉(zhuǎn)換為相位調(diào)制噪聲,又稱為孔徑抖動(dòng)。這種行為就像外部時(shí)鐘上的抖動(dòng),遵循公式2 ,孔徑抖動(dòng)(taperture-jitter)代替時(shí)鐘抖動(dòng)(tclock-jitter)。由公式2可以看出,隨著采樣的IF頻率(fanalog)增加,SNR下降。

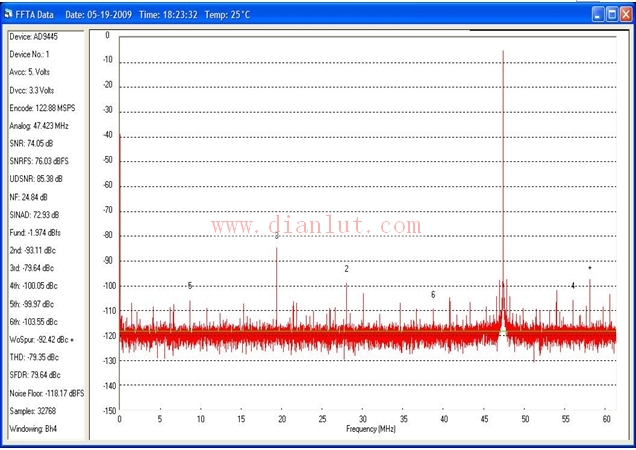

圖2顯示了14位ADC采樣170MHz中頻信號(hào)的FFT波形。在這種情況下所用的外部時(shí)鐘是源自頻譜純凈的Wenzel實(shí)驗(yàn)室參考振蕩器,驅(qū)動(dòng)著帶高壓擺率輸出信號(hào)的低抖動(dòng)矩形波整形電路。測量的意圖是盡量減少時(shí)鐘的影響,并確定由于ADC效應(yīng)所達(dá)到的SNR.由此產(chǎn)生的相對滿量程輸入信號(hào)的SNR測量數(shù)據(jù),在圖中標(biāo)示為SNRFS,是76db.這與ADC數(shù)據(jù)手冊1是一致的。

圖2:14位ADC的FFT波形。模擬輸入頻率= 170MHZ,時(shí)鐘頻率= 122.88MHz.SNRFS =76db.

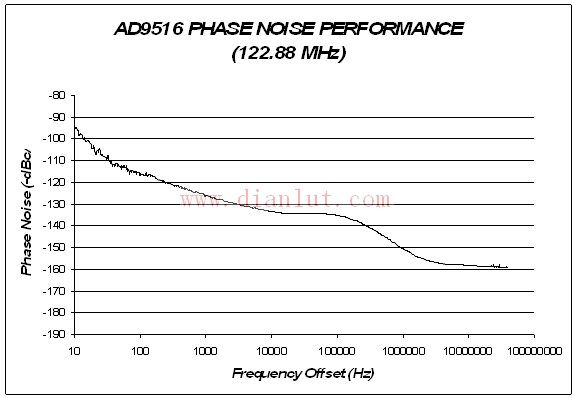

現(xiàn)在,我們將使用一個(gè)適合實(shí)際收發(fā)卡時(shí)鐘應(yīng)用的內(nèi)置VCO的時(shí)鐘IC.為了估算這一時(shí)鐘信號(hào)對ADC性能產(chǎn)生的影響,我們可以先測量時(shí)鐘電路的相位噪聲。其相位噪聲曲線如圖3所示。

圖3 :時(shí)鐘IC在122.88MHz下的相位噪聲

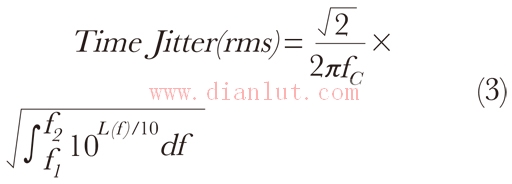

在給定的頻率范圍內(nèi),我們可以使用下列公式來將相位噪聲轉(zhuǎn)換成時(shí)間抖動(dòng)。

該公式本質(zhì)上是對相位誤差在目標(biāo)頻率范圍內(nèi)進(jìn)行積分并從一個(gè)相對2π的積分弧度誤差轉(zhuǎn)換成均方根時(shí)間誤差。

將圖3的相位噪聲數(shù)據(jù)代入公式3,在50kHz至61MHz的頻率范圍內(nèi),會(huì)得出230fs的抖動(dòng)值。50kHz至61MHz頻率范圍是用來對應(yīng)有效的FFT測量范圍,后者將用于檢驗(yàn)抖動(dòng)對所測SNR的影響的估算是否準(zhǔn)確。低至50kHz是源于FFT的有效二進(jìn)制間距,高至61MHz是奈奎斯特頻率。將得出的230fs抖動(dòng)代入公式1則得出72.2db的SNR值。

然而,實(shí)際達(dá)到的SNR將受到該抖動(dòng)和固有ADC噪聲的共同影響。圖2 FFT波形的SNR(76db)與根據(jù)時(shí)鐘抖動(dòng)得出的估算值(72.2db)的和平方根將得出70.68db的復(fù)合SNR.

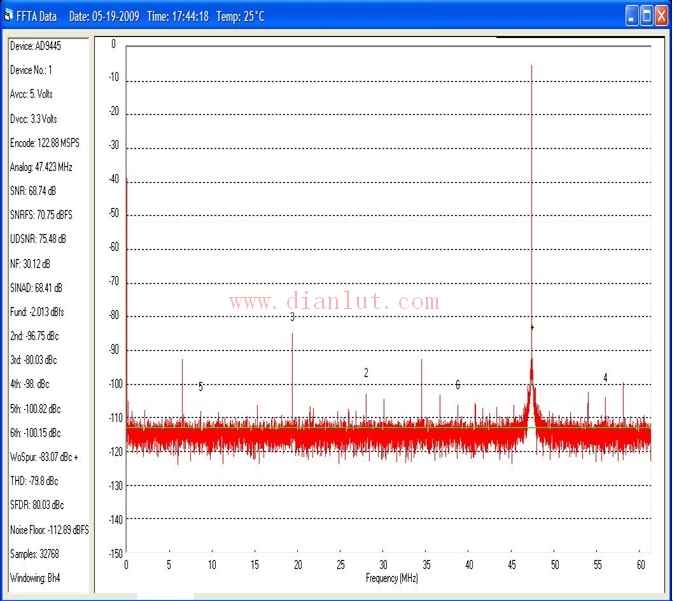

為了檢驗(yàn)這一估算值,圖4顯示了采用此時(shí)鐘IC作為采樣時(shí)鐘的相應(yīng)ADC FFT波形。所達(dá)到的SNR接近基于時(shí)鐘抖動(dòng)的估算值,體現(xiàn)了時(shí)鐘抖動(dòng)對ADC性能的影響至關(guān)重要。

圖4:采用時(shí)鐘IC的14位ADC的FFT波形。模擬輸入頻率= 170MHZ,時(shí)鐘頻率= 122.88MHz.SNRFS =70.75db.

應(yīng)該強(qiáng)調(diào)的是,公式2中的抖動(dòng)是寬帶均方根抖動(dòng)。抖動(dòng)帶寬有時(shí)被認(rèn)為是ADC編碼輸入的有效帶寬。由于該ADC是個(gè)采樣系統(tǒng),編碼輸入的寬帶噪聲在奈奎斯特頻帶內(nèi)可能被混疊多次。被混疊的抖動(dòng)帶寬的有效數(shù)字等于將奈奎斯特帶寬除以編碼輸入的帶寬。(見參考文獻(xiàn)3提供的詳細(xì)方案)。但如果時(shí)鐘邊沿的壓擺率很快速,在編碼輸入處噪聲電壓到時(shí)間誤差(抖動(dòng))的轉(zhuǎn)換將被衰減。通過在編碼輸入之前改善時(shí)鐘邊沿和保持很高的壓擺率可獲得的性能。在這些條件下,將抖動(dòng)進(jìn)行高達(dá)奈奎斯特頻率的積分就可提供一個(gè)合理的估算,因?yàn)樯鲜鱿嚓P(guān)性表明了該時(shí)鐘抖動(dòng)對ADC SNR的影響。

盡管上述討論的重點(diǎn)是ADC,本底噪聲和DAC的SNR由于高抖動(dòng)采樣時(shí)鐘會(huì)以類似方式下降。

采樣時(shí)鐘的寬帶抖動(dòng)并不是采樣時(shí)鐘頻譜純度的需要考慮的方面。"近載波"(close-in)相位噪聲3也會(huì)影響系統(tǒng)性能。

這種效應(yīng)類似于模擬混頻過程中的相位噪聲相互混頻。轉(zhuǎn)換器的編碼過程本質(zhì)上是復(fù)制混頻過程。編碼時(shí)鐘和模擬輸入信號(hào)在時(shí)域中相乘。這相當(dāng)于在頻域中進(jìn)行大家熟知的卷積。如圖5所示,其結(jié)果是造成在編碼時(shí)鐘上的任何相位噪聲裙緣將被復(fù)制在采樣輸入信號(hào)上。基于編碼率和采樣信號(hào)之間的頻率比例,關(guān)于每個(gè)載波幅度的相對相位噪聲將被修改。一個(gè)強(qiáng)相鄰信道信號(hào)的相位噪聲裙緣擴(kuò)展到一個(gè)有用弱信道時(shí),并有效地使后者失真,問題就出現(xiàn)了。圖6的FFT波形體現(xiàn)了這種效應(yīng)。在此圖中,一個(gè)ADC采樣一個(gè)小的有用信號(hào),但存在很強(qiáng)的相鄰干擾,干凈時(shí)鐘條件和高相位噪聲條件相重疊。可以看出,時(shí)鐘的相位噪聲裙緣在強(qiáng)干擾上被復(fù)制,并擴(kuò)展到有用信號(hào)的頻帶中。取決于所采用的調(diào)制標(biāo)準(zhǔn),相位噪聲頻率偏移可從數(shù)十kHz擴(kuò)展至數(shù)MHz.

圖5 :頻譜分析儀波形圖:層疊在干凈時(shí)鐘上的帶高相位噪聲的編碼。

圖6 :強(qiáng)干擾的相位噪聲擴(kuò)展到“有用”信號(hào)頻段。

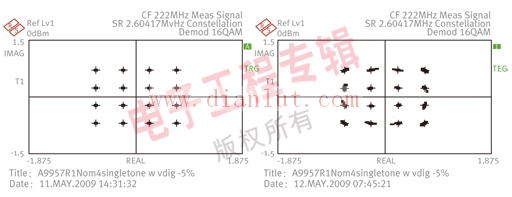

采樣時(shí)鐘相位噪聲對DAC的影響通常表現(xiàn)為調(diào)制信號(hào)的誤差向量幅度(EVM)有所降低。對于給定的調(diào)制方案,高相位噪聲有效地影響星座點(diǎn)使EVM下降并潛在地提高了誤碼率。圖7所示的16 QAM星座圖中體現(xiàn)了這一點(diǎn)。圖7(a)展示了干凈時(shí)鐘條件下的星座圖。圖7(b)展示了高相位噪聲時(shí)鐘對星座圖的影響。相位噪聲事實(shí)上旋轉(zhuǎn)了降低相鄰點(diǎn)噪聲容限的星座點(diǎn)有效相位。應(yīng)當(dāng)注意的是,寬帶相位噪聲和抖動(dòng)也會(huì)降低EVM.在帶通濾波用于DAC輸出的應(yīng)用中,主要的考慮事項(xiàng)就是近載波相位噪聲。

圖7:(a)干凈時(shí)鐘的16QAM星座圖。(b) 帶高相位噪聲的時(shí)鐘對星座圖的影響。

顯然,時(shí)鐘的頻譜純度是收發(fā)器時(shí)鐘解決方案的一個(gè)關(guān)鍵方面,但人們還期望時(shí)鐘系統(tǒng)能提供其他一些功能。

回到圖1可看到,該收發(fā)器具有多個(gè)接收通道,每個(gè)都需要單獨(dú)的ADC.在某些情況下,也會(huì)使用多個(gè)DAC通道。可能需要額外的時(shí)鐘通道來為用于數(shù)字預(yù)失真、FPGA或基帶ASIC芯片的ADC提供時(shí)鐘。

DAC和ADC編碼率通常各不相同。FPGA和基帶元器件也可能需要不同的頻率。頻譜干凈的主時(shí)鐘信號(hào)需要單獨(dú)分配給每個(gè)通道,為該通道分頻為所需的頻率,然后轉(zhuǎn)換成適當(dāng)?shù)妮敵鲂盘?hào)格式。單一收發(fā)卡的輸出信號(hào)通常混合了LVPECL、LVDS和CMOS格式。兩個(gè)通道之間往往要求偏斜很緊密,以限制PCB布線的延遲變化。在某些情況下,在兩個(gè)時(shí)鐘之間設(shè)置延遲或相位偏移是必要的。在轉(zhuǎn)換器采樣時(shí)鐘和用于將ADC輸出數(shù)據(jù)鎖存到基帶芯片的時(shí)鐘之間可能需要這樣做。

在這些系統(tǒng)中,通道與通道之間的耦合是一個(gè)需要考慮的因素。如前所述,DAC和ADC時(shí)鐘通常運(yùn)行于不同的頻率。通道之間的耦合,或時(shí)鐘從一個(gè)通道向另一個(gè)饋送可能會(huì)在采樣時(shí)鐘上導(dǎo)致不想要的雜散音。有用的時(shí)鐘信號(hào)和無用的噪聲可能會(huì)導(dǎo)致產(chǎn)生乘積混頻,這可能在有問題的地方產(chǎn)生毛刺。如果混頻發(fā)生在編碼輸入處,這些問題有時(shí)可通過在主時(shí)鐘和輸入時(shí)鐘邊沿及時(shí)進(jìn)行偏置而得到緩解。具備調(diào)節(jié)每個(gè)低抖動(dòng)時(shí)鐘延遲的能力可以成為時(shí)鐘系統(tǒng)的一項(xiàng)優(yōu)勢。

為了盡量減少系統(tǒng)宕機(jī)時(shí)間,在輸入?yún)⒖汲霈F(xiàn)故障的情況下,時(shí)鐘系統(tǒng)應(yīng)提供"備份"功能。這可通過增加第二個(gè)參考輸入來實(shí)現(xiàn),在主參考出錯(cuò)的情況可以切換到這個(gè)備份參考輸入。這種備份時(shí)鐘的指配有時(shí)被稱為"時(shí)鐘冗余".監(jiān)測主時(shí)鐘、檢測故障然后切換到備份的能力被稱為"參考切換"功能。

對于主時(shí)鐘和輔時(shí)鐘均出現(xiàn)故障的情況,可實(shí)施另一層保護(hù)功能,被稱為"保持(holdover)".在保持模式中,時(shí)鐘系統(tǒng)進(jìn)入一種模式,即在輸入失效之前盡可能長時(shí)間地保持時(shí)鐘頻率。對于給定的時(shí)鐘系統(tǒng),保持的準(zhǔn)確性和持續(xù)時(shí)間取決于時(shí)鐘電路架構(gòu)。本文第二部分在討論網(wǎng)絡(luò)時(shí)鐘時(shí)對此會(huì)有更詳細(xì)的闡述,因?yàn)槟切┫到y(tǒng)中的保持模式要嚴(yán)格得多。對于收發(fā)器系統(tǒng),保持模式并不試圖讓收發(fā)器工作在它的正常性能水平,而是要保持足夠的時(shí)鐘功能,如可生成適當(dāng)?shù)南到y(tǒng)警報(bào)以啟動(dòng)系統(tǒng)修復(fù)。

總而言之,多種多樣的系統(tǒng)需求廣泛存在,以支持各種各樣的空間標(biāo)準(zhǔn)、系統(tǒng)通道數(shù)要求和架構(gòu)方案。這些系統(tǒng)的時(shí)鐘必須足夠靈活,以適應(yīng)廣泛的應(yīng)用、保證系統(tǒng)可靠性并且還能夠提供轉(zhuǎn)換器所要求的極低抖動(dòng)和相位噪聲。

(1) AD9445:14位125MSPS , IF采樣ADC

(2)

![]()

(2)

(3) 采樣系統(tǒng)和時(shí)鐘相位噪聲和抖動(dòng)的影響。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- LM317:高效構(gòu)建電壓源及電流源電路方案1

- 如何使用多相轉(zhuǎn)換器平衡電流2

- LTC4365 如何實(shí)現(xiàn)敏感電路過壓與反接保護(hù)3

- MOS 管邏輯電路五種門電路特性4

- 點(diǎn)動(dòng)正轉(zhuǎn)控制電路簡介5

- 單鍵開關(guān)機(jī)電路與輕觸開關(guān)的創(chuàng)新設(shè)計(jì)解析6

- 二極管的恒壓降模型7

- MC34063電路計(jì)算公式及應(yīng)用講解8

- 3.3V - 1.8V 電平雙向轉(zhuǎn)換:多場景配置及獨(dú)特優(yōu)勢剖析9

- 液晶電視機(jī)電路結(jié)構(gòu)的關(guān)鍵要點(diǎn)10