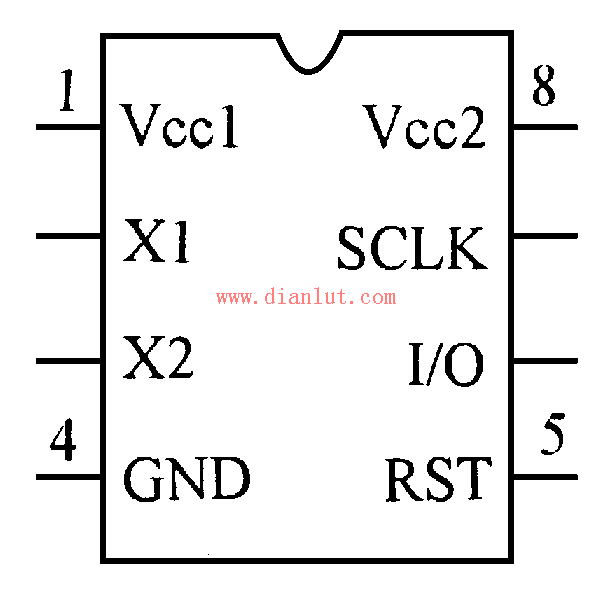

DS1302的引腳功能圖及其應(yīng)用電路

出處:chunyang 發(fā)布于:2011-08-23 12:35:56 | 15140 次閱讀

DS1302是一種高性能23621、低功耗、帶RAM的實時時鐘電路TDA2507T,它可以對年、月、日、周日、時、分、秒進(jìn)行計時,具有閏年補(bǔ)償功能,工作電壓為2.5V~5.5VMK005CL4.采用三線接口與CPU進(jìn)行同步通信,并可采用突發(fā)方式傳送多個字節(jié)的時鐘信號或RAM(RAM(隨機(jī)存取存儲器)RAM -random access memory 隨機(jī)存儲器。存儲單元的內(nèi)容可按需隨意取出或存入,且存取的速度與存儲單元的位置無關(guān)的存儲器。這種存儲器在斷電時將丟失其存儲內(nèi)容,故主要用于存儲短時間使用的程序。 按照存儲信息的不同,隨機(jī)存儲器又分為靜態(tài)隨機(jī)存儲器(Static RAM,SRAM)和動態(tài)隨機(jī)存儲器(Dynamic RAM,DRAM)。)數(shù)據(jù)。DS1302內(nèi)部有一個31×8的用于臨時性存放數(shù)據(jù)的RAM寄存器。DS1302是DS1202的升級產(chǎn)品,與DS1202兼容,但增加了主電源/后背電源雙電源引腳,同時提供了對后背電源進(jìn)行涓細(xì)電流充電的能力。

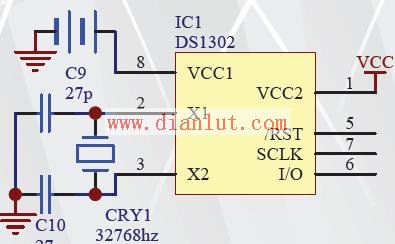

ds1302引腳功能及結(jié)構(gòu) 圖1示出DS1302的引腳排列,其中Vcc1為后備電源,VCC2為主電源。在主電源關(guān)閉的情況下,也能保持時鐘的連續(xù)運行。DS1302由Vcc1或Vcc2兩者中的較大者供電。當(dāng)Vcc2大于Vcc1+0.2V時,Vcc2給DS1302供電。當(dāng)Vcc2小于Vcc1時,DS1302由Vcc1供電。X1和X2是振蕩源,外接32.768kHz晶振。RST是復(fù)位/片選線,通過把RST輸入驅(qū)動置高電平來啟動所有的數(shù)據(jù)傳送。RST輸入有兩種功能RFBLN2012090A1T:首先,RST接通控制邏輯,允許地址/命令序列送入移位寄存器SMBJ70A-TR;其次,RST提供終止單字節(jié)或多字節(jié)數(shù)據(jù)的傳送手段。當(dāng)RST為高電平時,所有的數(shù)據(jù)傳送被初始化,允許對DS1302進(jìn)行操作。如果在傳送過程中RST置為低電平,則會終止此次數(shù)據(jù)傳送,I/O引腳變?yōu)楦咦钁B(tài)。上電運行時,在Vcc≥2.5V之前,RST必須保持低電平。只有在SCLK為低電平時,才能將RST置為高電平。I/O為串行數(shù)據(jù)輸入輸出端(雙向),后面有詳細(xì)說明。SCLK始終是輸入端。

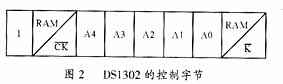

2.2 DS1302的控制字節(jié) DS1302 的控制字如圖2所示。控制字節(jié)的有效位(位7)必須是邏輯1,如果它為0,則不能把數(shù)據(jù)寫入DS1302中,位6如果為0,則表示存取日歷時鐘數(shù)據(jù),為1表示存取RAM數(shù)據(jù)GRM1886T1H1R0CD01C;位5至位1指示操作單元的地址;有效位(位0)如為0表示要進(jìn)行寫操作,為1表示進(jìn)行讀操作,控制字節(jié)總是從位開始輸出。

ds1302應(yīng)用電路

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。