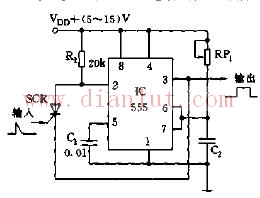

基于555集成芯片構成可控硅控制的觸發(fā)器電路

出處:xwj 發(fā)布于:2011-08-27 21:31:01 | 3101 次閱讀

如圖所示,555和R1、RP1、C2等組成觸發(fā)延時電路。平時,由于R1接VDD,使555處于復位狀態(tài),即3腳呈低電平;當觸發(fā)信號到來時,SCR導通,2腳有一低電平信號,使555翻轉置位,輸出高電平,暫穩(wěn)寬度為τ=1.1RP1C2。觸發(fā)后,SCR關斷。這種電路可降低對觸發(fā)脈沖的要求。若用CMOS型555(或556),還可減小觸發(fā)電流。

版權與免責聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權均屬于維庫電子市場網(wǎng),轉載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關法律責任。

本網(wǎng)轉載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔此類作品侵權行為的直接責任及連帶責任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉載時,必須保留本網(wǎng)注明的作品出處,并自負版權等法律責任。

如涉及作品內(nèi)容、版權等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關權利。