數(shù)字信號教程

出處:維庫電子市場網(wǎng) 發(fā)布于:2023-02-23 17:12:29 | 465 次閱讀

數(shù)字電路通常工作在有噪聲和電磁干擾的環(huán)境中。此外,將現(xiàn)代系統(tǒng)的工作頻率提高到 30MHz 以上會導致射頻 (RF) 范圍內(nèi)的現(xiàn)象,將數(shù)字電路轉(zhuǎn)換為高噪聲源。這種噪聲通過傳輸線上的耦合產(chǎn)生,并降低數(shù)字信號的質(zhì)量,從而導致操作錯誤。

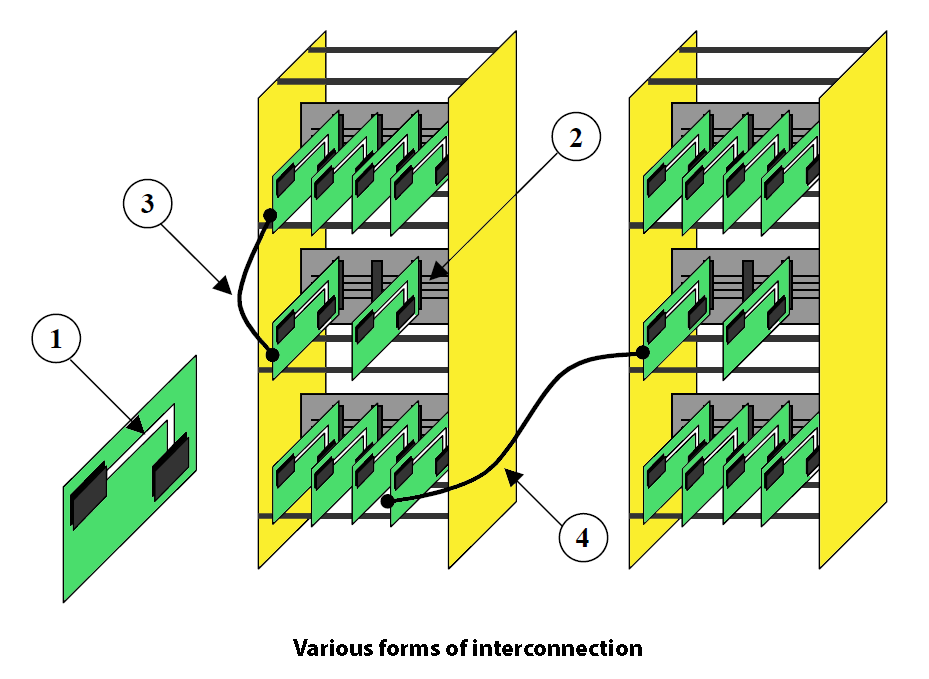

數(shù)字信號在同一印刷電路 (1) 上的不同集成電路之間、子系統(tǒng)與基板 (2) 之間、同一系統(tǒng)的子系統(tǒng) (3) 之間以及不同系統(tǒng)之間的傳輸過程中(圖 5.1)容易受到噪聲的影響(4). 為了覆蓋更長的距離,數(shù)字信號使用調(diào)制方法通過網(wǎng)絡傳輸。

多種形式互聯(lián)

圖 5-1

在傳輸過程中保持數(shù)字信號的完整性對于系統(tǒng)的安全運行至關重要。本章分析了現(xiàn)代數(shù)字電路中產(chǎn)生噪聲的主要原因,并提出了解決這些問題的方法。

在集成電路間的信號傳輸中,合理電荷的變化所產(chǎn)生的噪聲起著特殊的作用。這種噪聲是由流向和流出驅(qū)動電路的電流引起的,并且會影響傳輸信號的電平。

隨著數(shù)字電路速度的增加,在信號傳輸導體中出現(xiàn)“模擬”現(xiàn)象,如電壓前沿反射。這些反射會導致邏輯信道的振蕩和錯誤的信號接收。

在現(xiàn)代數(shù)字系統(tǒng)中,各種子系統(tǒng)通過公共通道進行邏輯互連所扮演的重要角色。用于驅(qū)動特定特性所需的數(shù)字電路的互連通道。

我們將研究相鄰信號導體相互作用的影響。這種相互作用是由于寄生電容和電感耦合造成的,是產(chǎn)生噪聲的主要原因。

最后,在最后一節(jié)中,我們將討論通過一對相同但極性相反的信號進行差分傳輸?shù)幕驹怼2顒觽鬏斂乖肽芰姡m用于長管道。

噪音輸出水平

在任何數(shù)字電路中,輸出級(驅(qū)動)在后續(xù)電路中起著信號傳輸?shù)闹饕饔谩Ec集成電路內(nèi)部邏輯的其余部分不同,輸出級需要在極短的時間內(nèi)具有特殊的供電或吸收功率的能力,才能成功引出與這些負載相關的負載。

隨著現(xiàn)代數(shù)字電路速度的提高,輸出電平中電流的切換速率也會增加。在高工作頻率下,流經(jīng)輸出級的電流的突然變化會產(chǎn)生噪聲印象。

在接下來的段落中,我們將看到產(chǎn)生 這種電流的原因 ,它會導致噪聲機制和應對方法。

峰值圖騰柱電流(交叉電流)

圖 5.2 顯示了一個典型的 CMOS 輸出級。兩個晶體管(pMOS 和 nMOS)連接電源線 (V + ) 或接地 (GND) 的輸出作為輸出值。幾乎相同的情況發(fā)生在帶有雙極結型晶體管的輸出級電路中。

圖騰柱電流峰值

圖 5-2

當將輸出值從一種狀態(tài)更改為另一種狀態(tài)時,兩個晶體管都會在短時間內(nèi)導通。直接影響是直接從電源電壓到地的泄漏電流峰值 (I S )的出現(xiàn)。該電流通常稱為圖騰柱電流,因為它是圖騰柱配置中步進晶體管對的特征。

如圖 5-2 所示,圖騰柱電源的拾取大約發(fā)生在輸出電壓從一種邏輯狀態(tài)轉(zhuǎn)換到另一種邏輯狀態(tài)的中間。

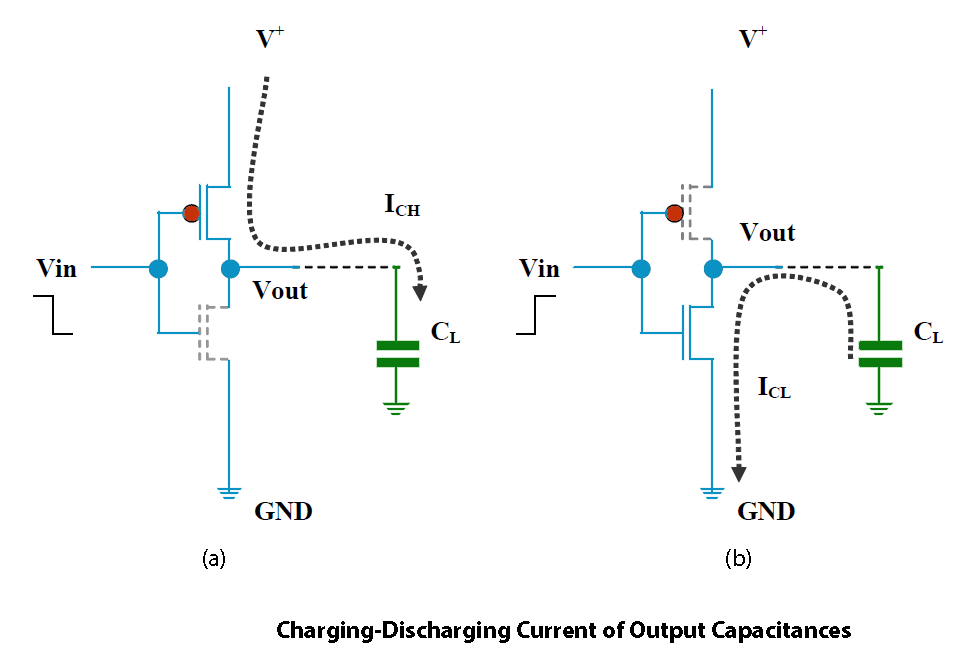

充電電流/放電容量輸出

除了將輸出從一種邏輯狀態(tài)切換到另一種邏輯狀態(tài)時的圖騰柱電流峰值外,輸出級還流過對內(nèi)部和外部電容進行充電或放電的電流。內(nèi)部電容在同一輸出級中形成,而外部電容來自連接到輸出級的驅(qū)動電路輸入端的容性負載(每個數(shù)字輸入呈現(xiàn) 2pF 至 10pF 的電容,具體取決于所使用的技術)。圖 5-3 此容量象征性地表示為電容器 C L。

輸出電容充放電電流

圖 5-3

當將輸出從邏輯低電平切換到邏輯高電平時(圖 5-3a),電容 C L由電壓 V +充電。在從高邏輯電平轉(zhuǎn)換到低邏輯電平的情況下會發(fā)生相反的情況:電容 C L通過地放電。流經(jīng)輸出級的電流量由以下公式給出:

Ι CL = C L ( dV / dt )

其中 dV 是高邏輯電平和低邏輯電平之間的電壓差。從這個關系可以看出,電容的充電/放電電流與邏輯高電平和低電平(電壓擺幅)的差異以及輸出電壓的速度變化(dt 項最小化)成正比。

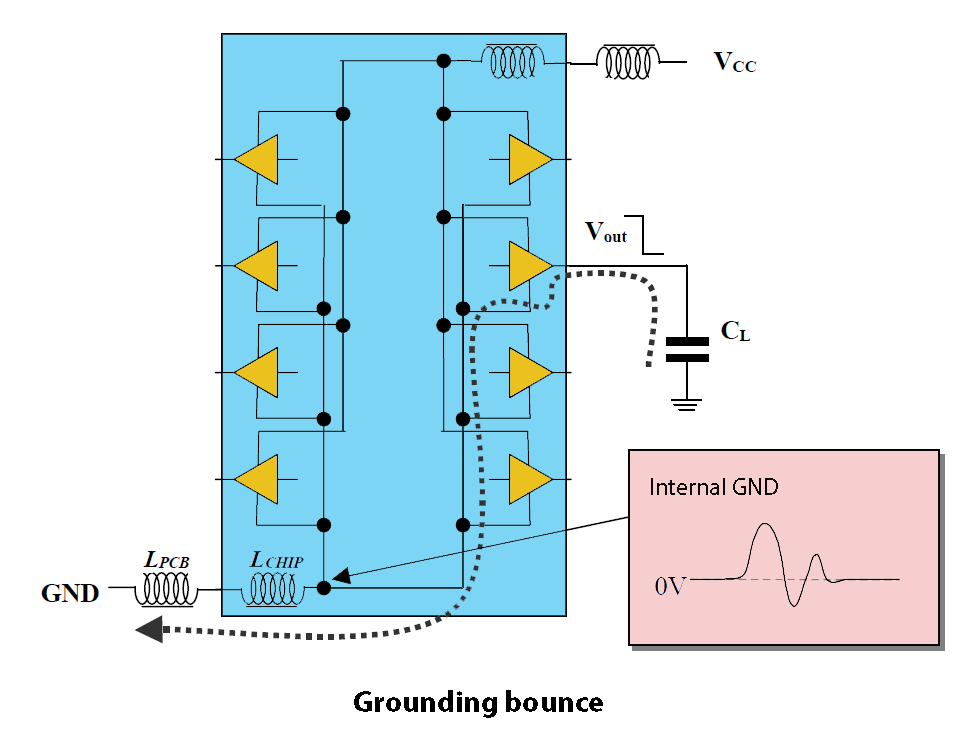

地彈

輸出電容充電或放電所需的電流和圖騰柱電流都流經(jīng)接地和電源端子。這些端子,作為集成電路的所有輸入和輸出端子,在內(nèi)部二氧化硅表面(裸片)和封裝(封裝)之間表現(xiàn)出寄生電感。硅表面的每個輸入/輸出都通過內(nèi)部框架中的導體(電線)連接,而這又連接到外部端子。界面的每一部分,都呈現(xiàn)出一定的電感值。每種封裝類型對每個端子的電感值不同,如表1.5所示:

包裝

每個終端的電感

PDIP

13.7nH

PLCC

10nH

SOIC

8.5 毫微

質(zhì)量標準作業(yè)程序

3.6nH

FC-BGA

1nH

表 5-1

寄生電感也出現(xiàn)在連接集成電路端子和中央電源的電路線 (PCB) 中。圖4.5中內(nèi)部電感表示為L CHIP,而電路的電感表示為L PCB。

接地反彈

圖 5.4

在圖 5-4 的示例中,隨著邏輯輸出從高電平變?yōu)榈碗娖剑娏髁苛飨蚪拥囟?GND。根據(jù)以下公式,該電流流導致寄生電感 L CHIP和 L PCB產(chǎn)生電勢 (V) :

V = L ( dI / dt)

該電勢暫時將硅表面的內(nèi)部電壓 GND 增加到大于 0V 的水平。一旦電流減少,內(nèi)部 GND 的波紋就會穩(wěn)定下來。

這種現(xiàn)象稱為地彈(ground bounce),會導致數(shù)字電路的運行出錯。現(xiàn)代高速電路中的電位差可能超過 1V。

相應地,隨著接地反彈的發(fā)生,內(nèi)部電源電壓 (V CC ) 會發(fā)生成比例的電壓變化。但是因為大多數(shù)邏輯系列使用接地作為參考電壓并且相對于邏輯高電平具有更大的容差,所以在這種情況下反彈 V CC被認為是次要的。

當同時改變同一集成電路的多個輸出時,接地反彈特別強,因為它會成倍增加流向/流出接地/電源端子的電流幅度。由于這個原因,產(chǎn)生的噪聲通常被稱為(同步開關噪聲 - SSN)。邏輯輸出的同步變化是通過中央時鐘脈沖計時的數(shù)字系統(tǒng)的主要特征。微控制器系統(tǒng)中同步輸出切換的一個典型示例是存儲器地址從 0FFFF(十六進制)到 10000(十六進制)的變化。

版權與免責聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關法律責任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔此類作品侵權行為的直接責任及連帶責任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負版權等法律責任。

如涉及作品內(nèi)容、版權等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關權利。