SiC器件短路事件失效模型分析

出處:維庫電子市場網(wǎng) 發(fā)布于:2023-08-09 16:43:43 | 578 次閱讀

由于開關(guān)速度快和通態(tài)電阻低,SiC MOSFET 通常很容易因短路事件而損壞。3安徽工業(yè)大學(xué)電氣與信息工程學(xué)院的研究團(tuán)隊提出了兩種常用功率器件中 SiC 器件在短路事件中的失效模型:SiC MOSFET(Cree 的 N 溝道增強(qiáng)型 SiC MOSFET) )和 SiC JFET(通常采用英飛凌的 SiC JFET)。4

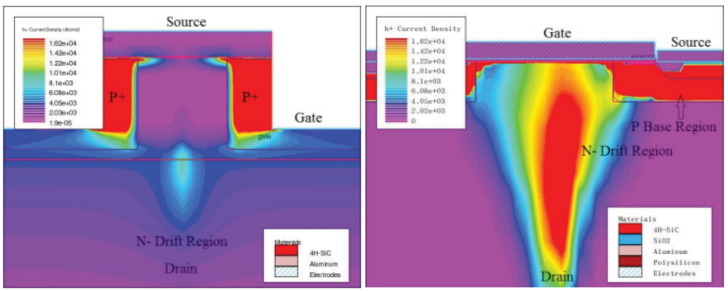

開發(fā) SiC 晶體管在短路事件中的故障模型

Wang等人提出的論文中研究表明,在短路事件下,故障電流高于功率器件的額定電流。5這意味著漏電流會導(dǎo)致故障電流,為了驗證這一點,使用了計算機(jī)輔助設(shè)計(TCAD)模擬技術(shù)。SiC JFET 和 SiC MOSFET 的電流分量描述了兩個 SiC 晶體管中的空穴電流密度。分析執(zhí)行的文件,我們可以得出結(jié)論,高密度空穴電流流過晶體管的N漂移區(qū)和P基極區(qū)之間的pn結(jié)。“TCAD仿真還表明,對于SiC MOSFET,高濃度載流子聚集在JFET區(qū)域的頂部;其中一小部分注入到柵極氧化物中,在高溫和高電場強(qiáng)度的應(yīng)力下形成柵極漏電流,”該團(tuán)隊解釋道。

故障 - 短路事件前 SiC JFET(上)和 SiC MOSFET(下)中空穴電流密度的分布

SiC JFET和 SiC MOSFET失效模型原理圖的設(shè)計考慮了漏電流的引入。虛線框中的結(jié)構(gòu)是傳統(tǒng)電路模型的一部分,與溝道電流I CH并聯(lián)的附加電流分量I DS_LK是跨過N漂移區(qū)和P基極區(qū)之間的pn結(jié)的漏電流。晶體管。在這項研究中,研究人員明確指出,由于柵極上沒有電壓偏置來開啟器件,因此沒有考慮 SiC JFET 的柵極漏電流。

SiC JFET(左)和 SiC MOSFET(右)的失效模型

通過pn結(jié)的漏電流的表達(dá)式由熱產(chǎn)生電流I th、雪崩電流I av和擴(kuò)散電流I diff組成。然而,對于柵極氧化物中的漏電流,已經(jīng)提出了幾種方法,團(tuán)隊考慮了福勒-諾德海姆(FN)隧道和普爾-弗倫克爾(PF)發(fā)射。因此電流 I FN和 I PF被認(rèn)為對 SiC MOSFET 柵極氧化物的漏電流有貢獻(xiàn)。

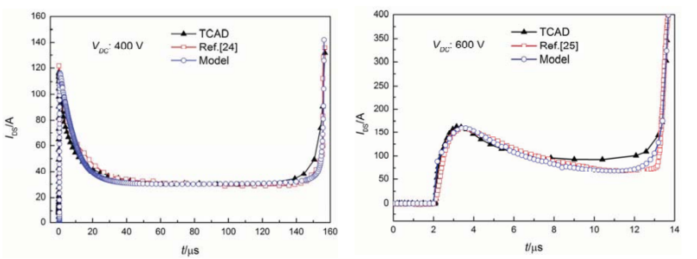

圖 3:SiC JFET(左)和 SiC MOSFET(右)故障模型驗證

對于SiC MOSFET的電路仿真,采用基于Shichman-Hodges物理模型的SPICE Level 1模型來描述截止區(qū)、線性區(qū)和飽和區(qū)三種模式,而對于SiC JFET,則采用Shockley物理模型:用過的。通常,在短路事件中,溝道中的電荷載流子受到較高電流應(yīng)力的影響,并且被加熱到相對于正常開關(guān)狀態(tài)更高的溫度。因此,溝道載流子的準(zhǔn)確遷移率模型對于理解載流子行為對晶體管短路性能的影響非常重要。

失效模型驗證

在短路故障情況下對所開發(fā)的 SiC JFET 和 SiC MOSFET 失效模型進(jìn)行了驗證,圖中顯示了從模型獲得的失效電流與論文中的結(jié)果的比較。6,7結(jié)果表明,在 400V 直流電壓下,SiC JFET 的短路故障時間 (tSC) 為 150μs,而在 600V 直流電壓下,SiC MOSFET 的短路故障時間 (tSC) 為 13μs。(編者注:圖 3 顯示了參考文獻(xiàn) 24 和 25,在本文中被視為參考文獻(xiàn) 6 和 7。)

“載流子遷移率取決于溫度和電場強(qiáng)度,對于準(zhǔn)確開發(fā) SiC 功率器件的故障模型是必要的,”該團(tuán)隊指出。“此外,通過改變I DS_LK的三個電流分量的組合方式,可以得到一個結(jié)論性的結(jié)果,即I TH決定了所開發(fā)的模型是否能夠模擬設(shè)備的故障。因此,短路期間產(chǎn)生的熱電流在故障效應(yīng)中起著至關(guān)重要的作用。”

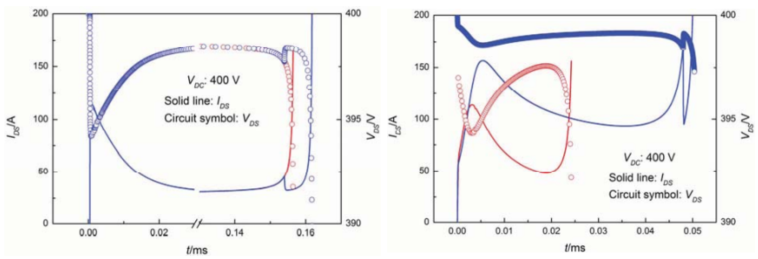

圖4:短路事件性能比較示意圖

短路故障情況下的驗證如圖所示,V DC為直流母線電壓,R S為電路環(huán)路雜散電阻,R G為柵極電阻,DUT 為器件(SiC JFET)或 SiC MOSFET)。圖中演示了兩種失效模式,紅色曲線為第一種失效模式,藍(lán)色曲線為第二種失效模式。注意到的一些參數(shù)是SiC JFET的失效時間比SiC MOSFET長得多,并且SiC JFET的飽和電流比SIC MOSFET低。這些變化的原因是載流子遷移率的溫度相關(guān)系數(shù)。

SiC JFET(左)和 SiC MOSFET(右)的兩種故障模式

該團(tuán)隊總結(jié)道:“對于立即失效,SiC JFET 表現(xiàn)出比 SiC MOSFET 更好的短路能力,并且 SiC JFET 的失效時間和臨界失效能量都高于 SiC MOSFET。” “對于延遲失效,在較低的直流母線電壓下,SiC JFET 的失效時間比 SiC MOSFET 長得多;然而,對于更高的直流母線電壓,兩個 SiC 晶體管的故障時間差異似乎很小。”

上一篇:MSGEQ7 電路圖和分線板

下一篇:電流差分緩沖放大器入門

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。