使用 UART 實現(xiàn) 1-Wire 總線主控

出處:維庫電子市場網(wǎng) 發(fā)布于:2023-09-28 17:35:09 | 631 次閱讀

然而,在 32 位系統(tǒng)中,處理器時鐘頻率通常超過 100MHz,并且使用 GPIO 引腳作為 1-Wire 總線主控器會消耗每個 1-Wire 位大量的時鐘周期。在 32 位便攜式系統(tǒng)中,在對 1-Wire 讀和寫時隙進行計時時會消耗寶貴的電池電量。一些系統(tǒng)通過在其芯片組中包含DS1WM可合成 1-Wire 總線主控* 硬件塊來減輕主處理器的位定時和字節(jié)成幀操作的負擔。如果DS1WM或其他硬件 1-Wire 主端口不可用,如果通用異步接收器發(fā)送器 (UART) 通道可用,則可以輕松完成與 1-Wire 器件的通信。

本應(yīng)用筆記包括所需電氣接口、UART 配置以及 UART 和 1-Wire 信號之間的時序關(guān)系的說明。假定您對 1-Wire 通信有一般性的了解。下面的討論中使用了典型的時序和邏輯電平,讀者應(yīng)參考特定的 1-Wire 器件數(shù)據(jù)手冊,了解具體的時序和電壓規(guī)格及容差。

概念概述

正確配置波特率、每個字符的數(shù)據(jù)位、奇偶校驗和停止位數(shù)量后,每秒 115,200 位的 UART 可以提供實現(xiàn) 1-Wire 主設(shè)備所需的輸入和輸出時序。UART 產(chǎn)生 1-Wire 復(fù)位脈沖以及讀和寫時隙。微處理器只需將一字節(jié)字符代碼放入 UART 發(fā)送寄存器以發(fā)送 1-Wire 1 或 0 位,然后 UART 即可完成工作。相反,微處理器讀取與從 1-Wire 從機讀取的 1 或 0 位相對應(yīng)的單字節(jié)字符代碼。所有 1-Wire 位傳輸都需要總線主控器 UART 通過將 1-Wire 總線驅(qū)動為低電平來開始周期。因此,每個 1-Wire 位周期包括 UART 的一個字節(jié)發(fā)送和一個字節(jié)接收。讀取時,接收到的數(shù)據(jù)是有意義的,但是寫入時,接收字節(jié)被丟棄。根據(jù) UART 的讀寫先進先出 (FIFO) 緩沖區(qū)深度,UART 還可以將 1-Wire 位構(gòu)建為字節(jié)值,進一步減少處理器開銷。

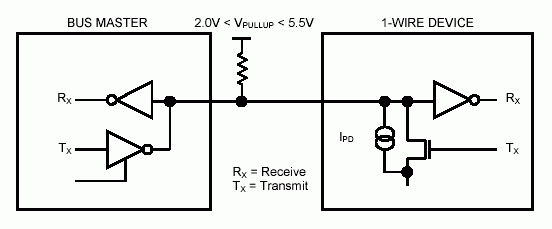

UART 至 1-Wire 電氣接口 1-Wire 器件在開漏環(huán)境中工作,總線電壓范圍為 2.0V 至 5.5V。精確的邏輯電平和最小上拉電壓取決于器件,但寄生電源器件通常需要 2.8V 的最小上拉電壓,以便在數(shù)據(jù)線處于低電平期間對用于供電的內(nèi)部存儲電容器進行充電。4.7kΩ 電阻器通常用作 1-Wire 數(shù)據(jù)線上的上拉電阻。該電阻器被動地提供邏輯高信號,而總線主設(shè)備和所有從設(shè)備驅(qū)動邏輯低信號。器件通常包含一個弱內(nèi)部下拉,如圖 1 中的 Ipd 所示。

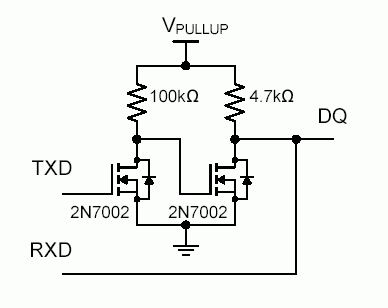

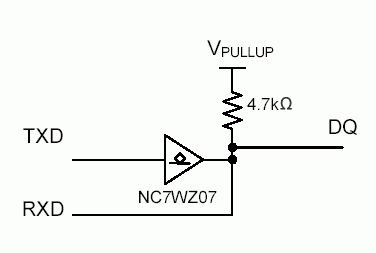

由于大多數(shù) UART 發(fā)送數(shù)據(jù)(TXD)引腳不是開漏引腳,因此通常需要外部開漏緩沖電路。該電路可以由分立元件構(gòu)成,如圖 2 所示,也可以使用如圖 3 所示的Fairchild NC7WZ07等集成解決方案。在這兩個電路中,4.7kΩ 上拉電阻在 1-Wire 總線上提供邏輯高電平。

分立開漏緩沖器。

集成開漏緩沖器。

版權(quán)與免責聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔此類作品侵權(quán)行為的直接責任及連帶責任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負版權(quán)等法律責任。

如涉及作品內(nèi)容、版權(quán)等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。