通過 LTspice 并行加載移位寄存器移動(dòng)數(shù)據(jù)

出處:維庫電子市場網(wǎng) 發(fā)布于:2024-07-11 16:33:55 | 656 次閱讀

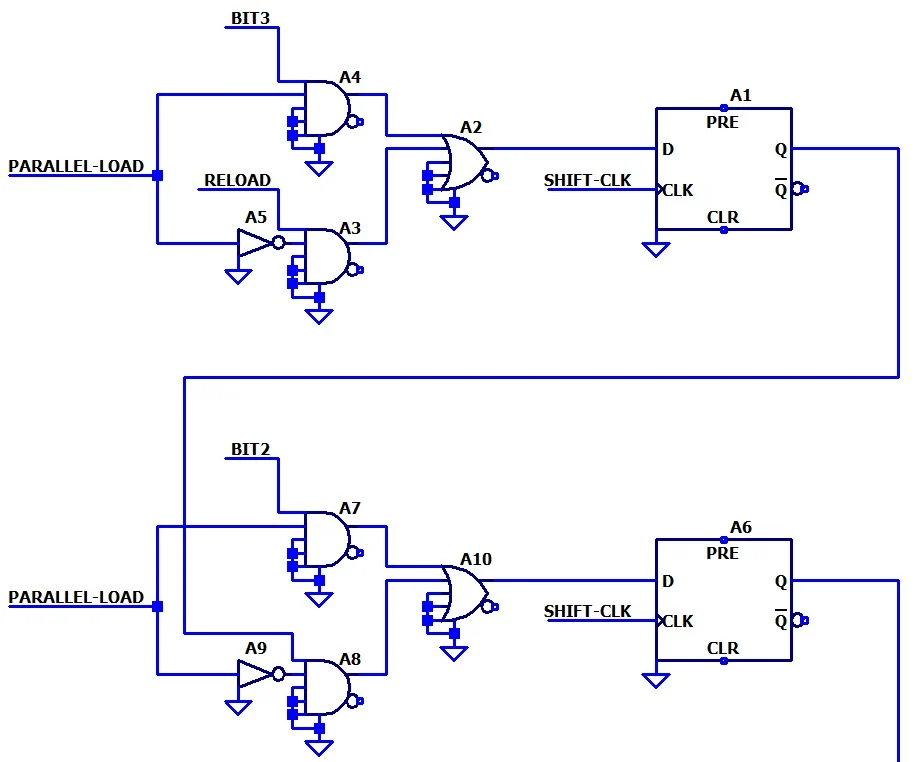

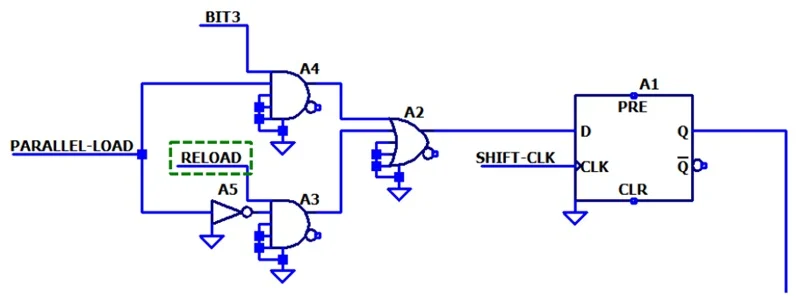

圖 1 傳達(dá)了寄存器內(nèi)存單元的結(jié)構(gòu)和互連。

LTspice 并行負(fù)載移位寄存器中的前兩個(gè)觸發(fā)器及其相關(guān)的邏輯門。 圖 1. LTspice 并行負(fù)載移位寄存器中的兩個(gè)觸發(fā)器及其相關(guān)的邏輯門。

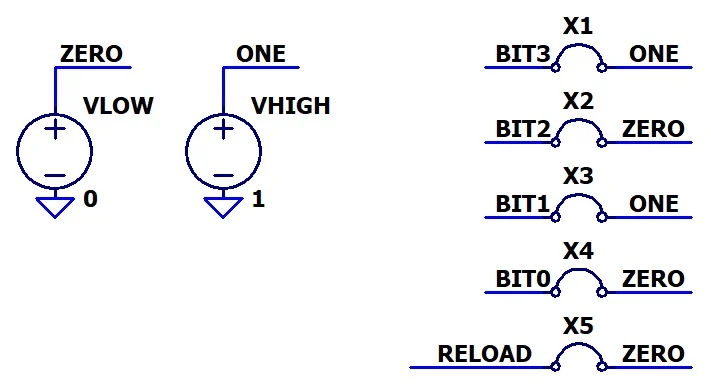

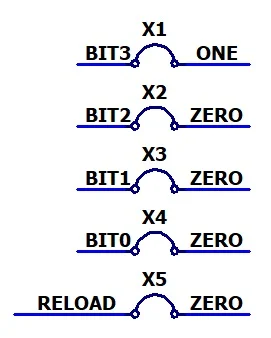

使用跳線創(chuàng)建數(shù)字?jǐn)?shù)據(jù) 您可能還記得上一篇文章,該寄存器是一個(gè)四位設(shè)備。原理圖中的每個(gè)四位都有一個(gè)名為BITn的輸入信號(hào),其中n是 0 到 3 范圍內(nèi)的整數(shù)。圖 2 顯示了我針對(duì)如何方便地為并行加載操作指定預(yù)選四位數(shù)字字的問題的解決方案。

圖 2.借助 LTspice 跳線元件分配并聯(lián)負(fù)載值。

標(biāo)記為 X1、2、3、4 和 5 的組件是跳線。跳線組件的用途主要是視覺上的,可在 LTspice 的“Misc”庫中找到。跳線符號(hào)傳達(dá)的概念與電路板上的物理跳線相同 - 它允許兩個(gè)名稱不同的網(wǎng)絡(luò)進(jìn)行電氣連接。

除了四個(gè)BIT信號(hào)外,還有RELOAD信號(hào)。如圖 3 所示,RELOAD是移位序列中第一個(gè)觸發(fā)器的主要輸入。這意味著RELOAD在其他位移出寄存器時(shí)保留移入寄存器的位。 寄存器中第一個(gè)觸發(fā)器的主輸入標(biāo)記為 RELOAD。

回頭參考圖 2,您會(huì)看到我已將RELOAD綁定到ZERO。這意味著一旦寄存器移出所有位,它就會(huì)變空(用零填充)。如果您希望寄存器重復(fù)移出預(yù)選序列,則可以將RELOAD連接到最后一個(gè)觸發(fā)器的輸出。

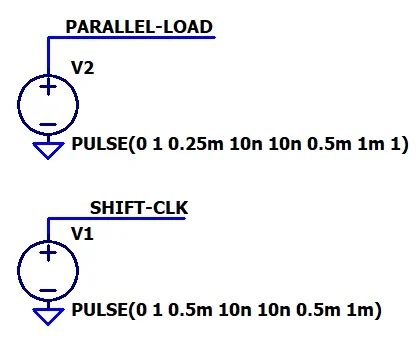

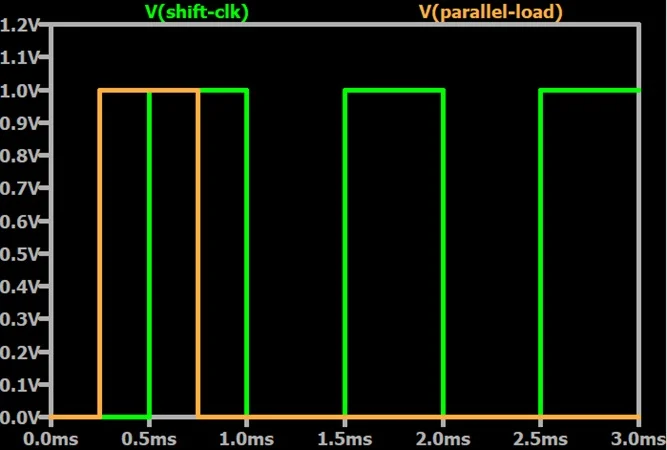

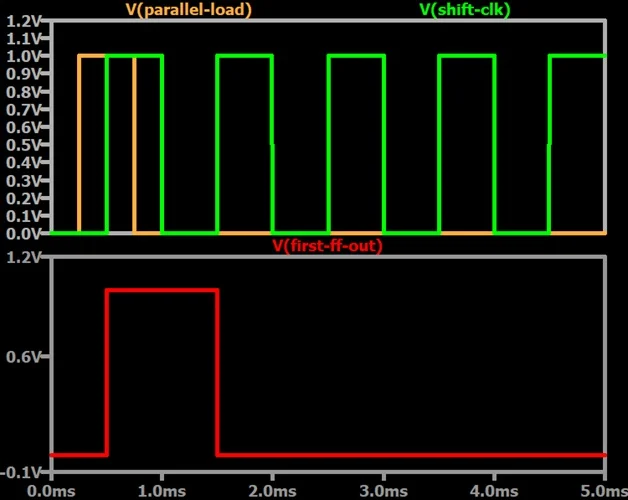

并行負(fù)載演示 圖 4 顯示了寄存器的兩個(gè)控制信號(hào)PARALLEL-LOAD和SHIFT-CLK的生成方式。由于我使用 PULSE 函數(shù)指定了 1 毫秒的周期,因此寄存器的移位頻率為 1 kHz。

圖 4. 生成寄存器的控制信號(hào)。移位頻率為 1 kHz。

如圖 5 所示,PARALLEL-LOAD信號(hào)在移位時(shí)鐘第一次從低到高的轉(zhuǎn)換過程中處于高電平有效狀態(tài)。因此,并行數(shù)據(jù)在系統(tǒng)的第一個(gè)時(shí)鐘周期內(nèi)加載到寄存器中。 輸出轉(zhuǎn)換顯示了移位時(shí)鐘和高電平有效的 PARALLEL-LOAD 信號(hào)之間的關(guān)系。

此后的每個(gè)時(shí)鐘周期,時(shí)鐘的上升沿都與出現(xiàn)在最后一個(gè)觸發(fā)器的輸出上的新的串行位相一致,這也是移位寄存器的輸出。

如果我們檢查圖 6 中的信號(hào)活動(dòng),我們可以更輕松地看到移位動(dòng)作。紅色軌跡表示序列中第一個(gè)觸發(fā)器的輸出。 第一個(gè)觸發(fā)器的輸出在加載邏輯高電平后,重新加載邏輯低電平。

注意FIRST-FF-OUT的兩個(gè)轉(zhuǎn)換如何與移位時(shí)鐘的上升沿一致。由于BIT3與ONE綁定,因此信號(hào)在第一次轉(zhuǎn)換時(shí)變?yōu)檫壿嫺唠娖健H缓螅捎赗ELOAD信號(hào)與ZERO綁定,因此它在第二次轉(zhuǎn)換時(shí)變?yōu)檫壿嫷碗娖健?br> 通過寄存器移位數(shù)據(jù)

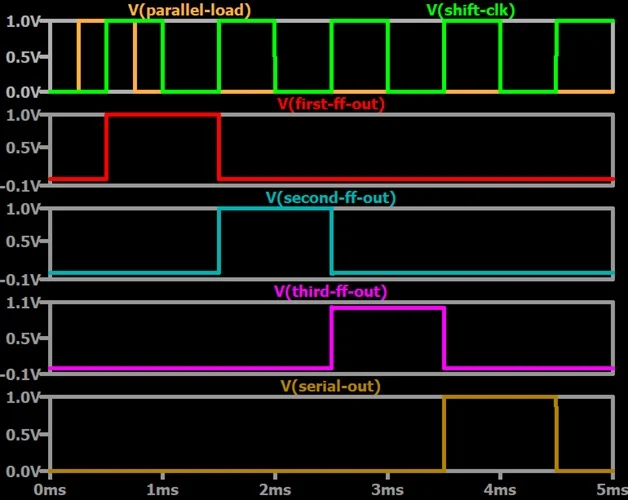

接下來,讓我們看看并行加載操作后會(huì)發(fā)生什么。對(duì)于此模擬,我使用圖 7 所示的跳線設(shè)置。我們的四位字現(xiàn)在不是 0101,而是 0001。 新模擬的跳線設(shè)置。BIT1 現(xiàn)在與 ZERO 綁定,而不是 ONE。

首先,BIT3被加載邏輯高電平值。圖 8 顯示了該邏輯高電平信號(hào)如何通過移位寄存器傳播——從BIT3到BIT2再到BIT1,最后到BIT0。 寄存器的四個(gè)觸發(fā)器的時(shí)序圖。

您可以通過觀察 1 毫秒整數(shù)倍的SERIAL-OUT來識(shí)別串行比特流。觸發(fā)器的輸出在時(shí)鐘的上升沿轉(zhuǎn)換;因此,我們希望在輸出信號(hào)穩(wěn)定的下降沿進(jìn)行采樣。

例如,上圖時(shí)序圖中的前三個(gè)上升沿分別與 0.5 毫秒、1.5 毫秒和 2.5 毫秒對(duì)齊。因此,正確的采樣時(shí)刻為 1 毫秒、2 毫秒和 3 毫秒。這由圖 9 中的白色虛線表示。 0001 以串行格式出現(xiàn)在最后一個(gè)觸發(fā)器的輸出上。

傳播延遲和模擬時(shí)間步長

正如我們在本系列文章前面所討論的那樣,在 LTspice 中準(zhǔn)確模擬數(shù)字電路有時(shí)需要我們指定自定義設(shè)備參數(shù)。在這種情況下,您需要指定傳播延遲和最大時(shí)間步長,以確保移位寄存器可靠工作。

LTspice 的默認(rèn)傳播延遲 ( T d ) 為零,這意味著信號(hào)從輸入瞬間傳播到輸出。沒有任何延遲,一個(gè)觸發(fā)器的輸出信號(hào)可以如此快速地改變狀態(tài),以至于序列中的下一個(gè)觸發(fā)器沒有時(shí)間響應(yīng)時(shí)鐘的上升沿來采樣信號(hào)。

結(jié)果是位不會(huì)通過寄存器傳播。您可以通過為每個(gè)觸發(fā)器指定合理的T d值來避免此問題。我使用了 1 μs,如圖 10 所示。

指定移位寄存器的時(shí)間延遲。

圖10.移位寄存器的時(shí)間延遲規(guī)格。

觸發(fā)器輸出信號(hào)上的振鈴是您可能遇到的另一個(gè)奇怪問題。如圖 11 所示。

第一個(gè)觸發(fā)器輸出上振鈴的示例。

圖 11.觸發(fā)器輸出轉(zhuǎn)換后振鈴的示例。

圖 12 中的特寫視圖讓我們更清楚地看到振蕩。

上圖中振蕩的放大視圖。

圖 12.圖 11 中的雜散振蕩的特寫。

振鈴是由 LTspice 仿真引擎與數(shù)字元件生成時(shí)間步長信息的方式之間的某種沖突引起的。我設(shè)法通過為仿真指定適當(dāng)?shù)淖畲髸r(shí)間步長來消除該問題。如圖 13 所示,我選擇的最大時(shí)間步長為 50 ns,這比我為觸發(fā)器選擇的 100 ns 上升/下降時(shí)間要短(圖 10)。

指定最大模擬時(shí)間步長。

圖 13.指定最大模擬時(shí)間步長。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- LM317:高效構(gòu)建電壓源及電流源電路方案1

- 如何使用多相轉(zhuǎn)換器平衡電流2

- LTC4365 如何實(shí)現(xiàn)敏感電路過壓與反接保護(hù)3

- MOS 管邏輯電路五種門電路特性4

- 點(diǎn)動(dòng)正轉(zhuǎn)控制電路簡介5

- 單鍵開關(guān)機(jī)電路與輕觸開關(guān)的創(chuàng)新設(shè)計(jì)解析6

- 二極管的恒壓降模型7

- MC34063電路計(jì)算公式及應(yīng)用講解8

- 3.3V - 1.8V 電平雙向轉(zhuǎn)換:多場景配置及獨(dú)特優(yōu)勢剖析9

- 液晶電視機(jī)電路結(jié)構(gòu)的關(guān)鍵要點(diǎn)10