實現(xiàn)高分辨率(16 位)DAC 的最高 8 位解決 PWM 遲鈍問題

出處:維庫電子市場網(wǎng) 發(fā)布于:2024-08-22 16:12:29 | 555 次閱讀

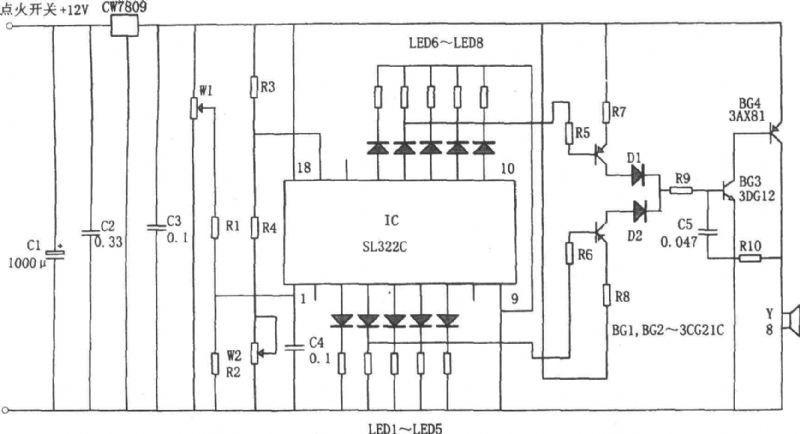

圖 1提供了一種解決 PWM 遲鈍問題的方案,即使用它來實現(xiàn)高分辨率(16 位)DAC 的最高 8 位,而另一種技術(shù)(數(shù)字電位器)提供低 8 位。然后,兩個輸出在一個簡單的 256:1 比例電阻分壓器中被動相加。這樣做的好處是穩(wěn)定速度提高了 256 倍(與使用 PWM 進行完整的 16 位計數(shù)相比),同時還具有 16 位分辨率、單調(diào)性、線性度(INL 和 DNL)和微伏零點穩(wěn)定性。該電路僅靠從單個 5V 電源軌吸取的幾 mA 電流運行,同時還集成了相當(dāng)不錯的電壓基準(zhǔn)。

有源低通模擬紋波減法濾波通過R1C1 + R2C2 網(wǎng)絡(luò)進行,如“使用模擬減法消除 PWM DAC 紋波”中所述。如果我們假設(shè)256/32 MHz = 8 ?s PWM 周期,則所示的4.99 kΩ x 0.1 ?F = 499 ?s RC 時間常數(shù)適用于 16 位 (96 dB) 紋波衰減。電容當(dāng)然需要根據(jù)不同的 PWM 時鐘頻率進行比例調(diào)整。

同時,1k Dpot U2 提供 SPI 控制、8 位分辨率、0 至 2.5v lsbyte 貢獻(xiàn),該貢獻(xiàn)通過 R2R3 分壓器以 256:1 的比例與 U1 的 PWM 輸出相加。R2:R3 比率應(yīng)準(zhǔn)確且穩(wěn)定,優(yōu)于 0.5%。R3 遠(yuǎn)高于電位器提供的 2.5k(最大)可變阻抗,因此其對非線性的貢獻(xiàn)保持小于 +/-? lsb。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。