電壓控制電路中 FET 的使用指南,第 5 部分

出處:維庫電子市場網(wǎng) 發(fā)布于:2024-09-19 17:17:02 | 681 次閱讀

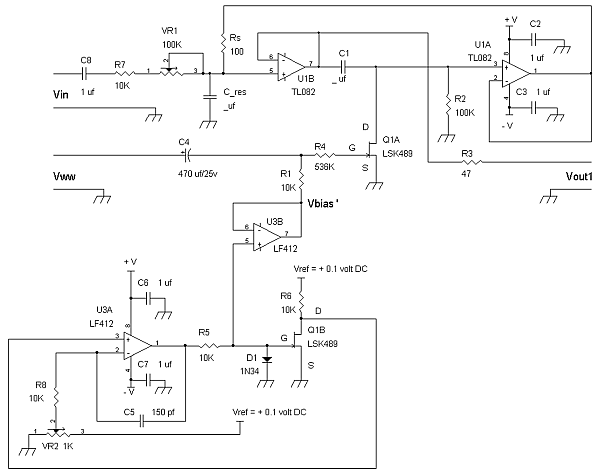

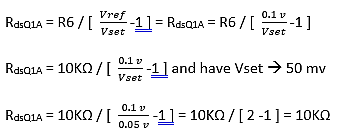

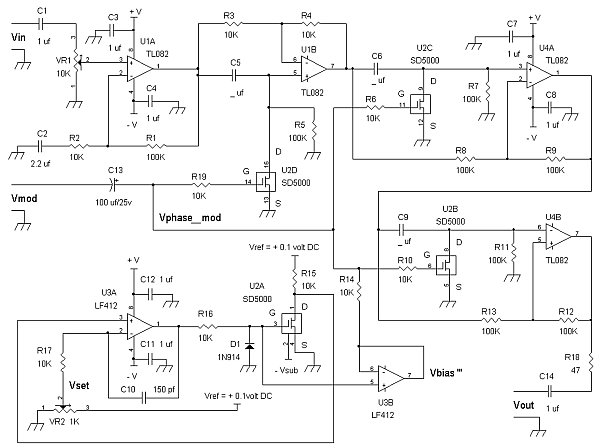

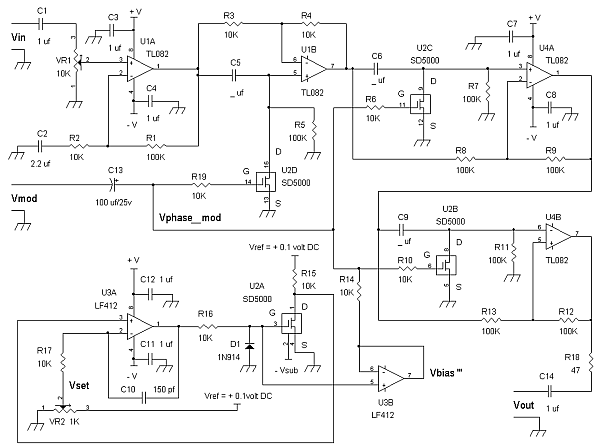

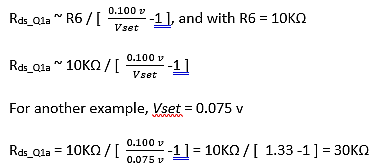

通過使用具有小直流偏置電壓 Vref = +100 mV DC 和已知負(fù)載電阻 R6 的參考 FET Q1B,我們可以通過電位器 VR2 引腳 2 將電壓設(shè)置為 R8,將 Q1B 偏置到任何漏極到源極電阻 R ds。 小直流電壓 Vref 設(shè)置為 +100 mV DC,以確保 Q1B 仍處于三極管或歐姆區(qū)域。如果我們將 VR2 的滑塊電壓設(shè)置為 Vset 以提供一半電壓或 +50 mV,這將導(dǎo)致偏置伺服電路打開 Q1B,直到其漏極電壓也為 +50 mV DC。如果我們通過 10KΩ 串聯(lián)電阻 R6 在 Q1B 的漏極獲得 +100 mV 的一半 = 50 mV,這意味著漏極到源極電阻也是 10KΩ。因為偏置伺服電路是一個負(fù)反饋電路,無論我們在 VR2 的滑塊上設(shè)置什么電壓,該滑塊都會耦合到 U3A 的 (-) 輸入,所以其 (+) 輸入必須通過輸入端子之間的虛擬短路跟隨該電壓。由于 (+) 輸入端子連接到 Q1B 的漏極,因此其漏極電壓必須與 VR2 滑塊上的電壓相匹配。補(bǔ)償電容器 C5 可確保電路不會振蕩。為了更好地抑制噪聲,C5 可以高達(dá) 1 uf。 當(dāng) Vset = VR2 引腳 2 處的電壓時,求解 Q1A 的 R ds的一般方程 為:

注意:二極管 D1 確保參考 FET 的柵極在開啟期間不會正向偏置。如果柵極正向偏置,偏置伺服電路可能會“卡住”。

就低失真而言,最大輸入信號幅度通常為峰峰值 150 mV。 現(xiàn)在讓我們看一下圖 41,哇音電壓控制帶通濾波器通過 Rfb 和 R4 帶有偏置伺服電路的降低失真反饋。

由于降低失真的反饋網(wǎng)絡(luò) Rfb 和 R4 對柵極的衰減約為 50%,因此放大器 U3B 的增益設(shè)置為 2 以補(bǔ)償這一點。請注意,R1

盡管增加 Q1B 的柵極電壓可使 Q1A 的 R ds接近相同 ,但對于 Q1A 和 Q1B 相同的柵極電壓,Q1A 的漏極至源極電阻實際上更低。原因是電阻網(wǎng)絡(luò) Rfb 和 R4 形成負(fù)反饋效應(yīng),略微降低了 Q1A 的 R ds。也就是說 R dsQ1A dsQ1B 略有降低。

盡管如此, 與手動操作相比,圖 41仍然提供了一種更簡單的偏置 FET 的方法。稍后我們將重新討論圖 41的更準(zhǔn)確方法 。 現(xiàn)在,讓我們看一下圖 42中的相移系統(tǒng)的偏置伺服電路。它使用與圖 40相同的偏置伺服電路,但這次使用 MOSFET 作為壓控電阻。請注意,D1 反向連接,以確保開啟時柵極到源極電壓不會對 N 通道增強(qiáng)器件產(chǎn)生過負(fù)的影響。

該電路的總相移為:

例如,Vset = 0.033 v = 引腳 2 VR2 處的電壓,則

請注意,–Vsub = ?5 伏至 ?10 伏直流電,以確保基板偏置正確。

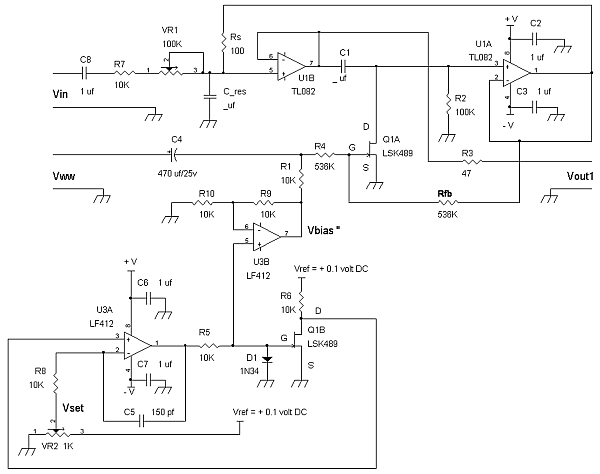

可以使用一個 1000 uf 電解電容器(其 (+) 端子位于 VR2 的引腳 2)將調(diào)制信號耦合到 VR2 引腳 2,而不是使用 Vww。 參見圖 43,改進(jìn)的伺服偏置電路。

為了更準(zhǔn)確地確定 Q1A 的 R ds ,偏置伺服電路通過 U4A 復(fù)制反饋網(wǎng)絡(luò),U4A“復(fù)制”U1A,R10 和 R9 復(fù)制 Rfb 和 R4。

我們還應(yīng)注意,盡管該電路可以更精確地設(shè)置正確的柵極偏置電壓,但由于 Rfb 和 R4 的負(fù)反饋效應(yīng),Q1A 的實際漏極至源極電阻會略低。因此,我們將使用“~”代替“=”表示近似值 偏置由 VR2 引腳 2 處的滑塊電壓 Vset 設(shè)置,使得:

注意: 通過將 FET 的漏極到源極電阻設(shè)置為更高的值,可以實現(xiàn)更低的失真。例如,我們將 R6 設(shè)置為 51KΩ 而不是 10KΩ,并將 R ds_Q1a 設(shè)置為 > 100KΩ 范圍。

對于圖 41 和 43中的 P 通道 JFET 器件,請使用負(fù) Vref(例如 – 100 mV DC)和反向二極管 D1 的連接。對于圖 42中的 P 通道 MOSFET ,請使用負(fù) Vref(例如 – 100 mV DC)和反向二極管 D1 的連接。

最后的建議和想法

DMOS 器件具有漏極至柵極電容非常低的優(yōu)勢。要使用雙列直插式封裝 (DIP) 中的這些器件(例如 SD5000 系列),請確保通過電阻(例如 1KΩ 至 10KΩ)偏置襯底引腳,電壓源的電壓應(yīng)比任何其他引腳上出現(xiàn)的電壓更負(fù)或更低。例如,如果最小源電壓為地,則襯底電壓應(yīng)為 ?2 伏至 ?9 伏。如果漏極和源極之間的交流信號很小,例如

有些 DMOS FET 的柵極電容非常低,并且沒有內(nèi)部齊納二極管的保護(hù),否則會增加更多的柵極電容。DMOS 器件(如 SD211 和 SD214)帶有短接導(dǎo)線。首先將柵極和源極引線焊接到提供從柵極到源極的直流路徑的電路上,然后可以移除短接導(dǎo)線。在短接導(dǎo)線完好無損的情況下,您可以在移除短接導(dǎo)線之前(但在將 DMOS FET 焊接到電路之前)在柵極和源極引線上焊接一個 10KΩ 電阻。

本文介紹了一些基本的電壓控制電路。這些電路可用于更復(fù)雜的系統(tǒng),例如吉他效果踏板。例如,圖 8 至 15中所示的帶反饋的電壓控制電阻電路也可以通過過驅(qū)動輸入信號用作對稱削波電路。沒有反饋的電壓控制衰減器電路(例如,通過移除圖 8 至 15中的 R3 )可以通過再次過驅(qū)動輸入信號用作非對稱削波器。這些削波電路可以并入電吉他模糊踏板中。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。