高速脈沖發(fā)生器具有可編程級(jí)別

出處:維庫(kù)電子市場(chǎng)網(wǎng) 發(fā)布于:2024-10-16 16:53:42 | 402 次閱讀

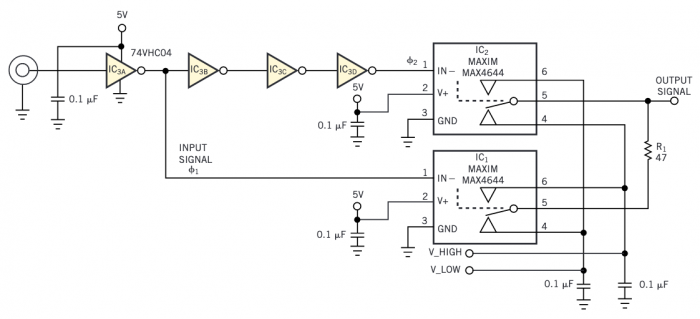

設(shè)計(jì)人員也將高速數(shù)字電路使用的亞微米工藝應(yīng)用于模擬開關(guān),因此這些開關(guān)的開啟和關(guān)閉時(shí)間也會(huì)產(chǎn)生快速的上升和下降時(shí)間。此外,SPDT(單刀雙擲)開關(guān)可以產(chǎn)生高電平和低電平可編程的脈沖。 模擬開關(guān)阻礙其用作脈沖發(fā)生器的一個(gè)特性是固有的內(nèi)置延遲(先斷后合時(shí)間),該延遲可保證 SPDT 開關(guān)在轉(zhuǎn)換期間不會(huì)將兩個(gè)開關(guān)端子短路在一起。不幸的是,這種延遲和開關(guān)的有限開啟時(shí)間也延長(zhǎng)了上升和下降時(shí)間。您可以通過向電路添加動(dòng)態(tài)上拉和動(dòng)態(tài)下拉來避免這種影響(圖 1)。足夠低的上拉和下拉阻抗可以極大地改善相應(yīng)的上升和下降時(shí)間。

考慮穩(wěn)態(tài)條件,其中 F 1較低且 F 2高。 IC 1的COM 引腳和IC 2的COM 引腳連接到V_LOW,F(xiàn) 1的上升沿導(dǎo)致IC 1將輸出信號(hào)拉高。由于串聯(lián)電阻R 1相對(duì)于MAX4644的導(dǎo)通電阻較大,即47W與2.5W典型值相比,因此對(duì)輸出電壓的直接影響很小。然而,當(dāng) F 1傳播通過反相器串時(shí),F(xiàn) 2的下降沿導(dǎo)致 IC 2從 V_LOW 轉(zhuǎn)變?yōu)?V_HIGH。低阻抗上拉電阻 R 1的存在為信號(hào)轉(zhuǎn)換提供驅(qū)動(dòng),隨后 IC 2很快閉合。

C55輸入信號(hào)為 5V 邏輯,輸出擺幅為 1 至 2V(圖 2)。您可以將 V_LOW 和 V_HIGH 設(shè)置為 IC 1和 IC 2電源范圍內(nèi)的任意電平。該電路的靜態(tài)電流基本上為零,僅在輸出轉(zhuǎn)換期間出現(xiàn)短暫的峰值。輸出的上升和下降時(shí)間約為 4 納秒,輸出阻抗為 2.5W。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫(kù)電子市場(chǎng)網(wǎng)”的所有作品,版權(quán)均屬于維庫(kù)電子市場(chǎng)網(wǎng),轉(zhuǎn)載請(qǐng)必須注明維庫(kù)電子市場(chǎng)網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請(qǐng)?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- LM317:高效構(gòu)建電壓源及電流源電路方案1

- 如何使用多相轉(zhuǎn)換器平衡電流2

- LTC4365 如何實(shí)現(xiàn)敏感電路過壓與反接保護(hù)3

- MOS 管邏輯電路五種門電路特性4

- 點(diǎn)動(dòng)正轉(zhuǎn)控制電路簡(jiǎn)介5

- 單鍵開關(guān)機(jī)電路與輕觸開關(guān)的創(chuàng)新設(shè)計(jì)解析6

- 二極管的恒壓降模型7

- MC34063電路計(jì)算公式及應(yīng)用講解8

- 3.3V - 1.8V 電平雙向轉(zhuǎn)換:多場(chǎng)景配置及獨(dú)特優(yōu)勢(shì)剖析9

- 液晶電視機(jī)電路結(jié)構(gòu)的關(guān)鍵要點(diǎn)10