發(fā)射極耦合邏輯的基礎(chǔ)知識

出處:維庫電子市場網(wǎng) 發(fā)布于:2024-12-25 10:42:02 | 560 次閱讀

本文將回顧基本 ECL 反相器/緩沖器的操作,然后我們將了解該邏輯系列的一些最重要的特性。

發(fā)射極耦合邏輯

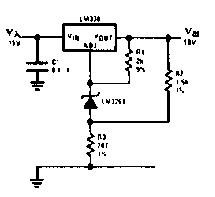

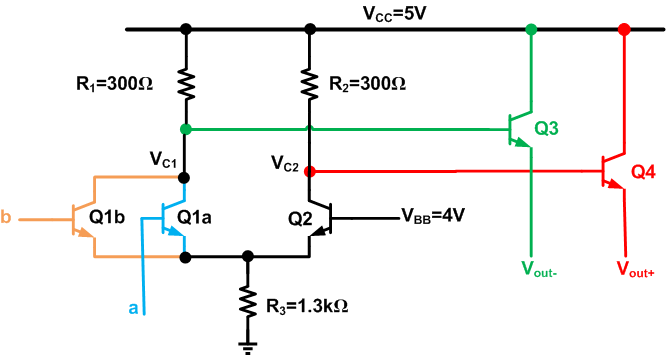

發(fā)射極耦合邏輯是高速雙極邏輯系列。為了熟悉這個邏輯,讓我們檢查一下如圖 1 所示的 ECL 反相器/緩沖器。在該圖中,$$V_{in}$$ 是門的輸入,$$V_{out-}$$ 是門的輸入。 $$V_{in}$$ 和 $$V_{out+}$$ 的反轉(zhuǎn)版本是 $$V_{out-}$$ 的補集。在此特定示例中,$$V_{out+}$$ 可以被視為輸入的緩沖版本。此外,$$V_{BB}$$是合適的電壓(圖1中的4V)。我們將邏輯高電平和邏輯低電平分別定義為 4.4 V 和 3.6 V,并檢查圖 1 中電路的工作情況。

假設 $$V_{in}$$ 為邏輯高電平 (4.4 V),因此 Q1 的發(fā)射極電壓約為 4.4-0.6=3.8 V。因此,Q2 的基極-發(fā)射極電壓將為 0.2 V。發(fā)射極電壓不足以開啟 Q2。因此,電阻器 R2 將把 Q2 的集電極上拉至 Vcc=5V。

為了計算集電極電壓$$V_{c1}$$,我們應該注意流經(jīng)R3的電流,即$$\tfrac{3.8V}{1.3k \Omega}=2.92mA$$,將流經(jīng)Q1 。因此,我們得到$$V_{c1} = 5V-300Ω\times 2.92mA=4.12V$$(為了簡化計算,我們假設集電極電流等于發(fā)射極電流)。射極跟隨器 Q3 和 Q4 將充當緩沖器,將 Q1 和 Q2 的(直流電平轉(zhuǎn)換)集電極電壓傳遞到 ECL 門的最終輸出 $$V_{out-}$$ 和 $$V_{out+}$ $。假設 Q3 和 Q4 的基極-發(fā)射極電壓為 0.6V,我們得到 $$V_{out+}$$=4.4V 和 $$V_{out-}$$=3.52V。如您所見,將邏輯高電平應用于輸入會在 $$V_{out+}$$ 處產(chǎn)生邏輯高電平,并且在 $$V_{out-}$$ 處產(chǎn)生非常接近定義的邏輯低電平 (3.6 V) 的電壓電平。因此,圖 1 的電路用作反相器/緩沖器。

如果我們將邏輯低電壓(3.6V)施加到柵極的輸入,Q2 將導通,Q1 將截止。這將導致 $$V_{out-}$$ 處的邏輯高電平和非常接近 $$V_{out+}$$ 處的邏輯低電平 (3.61 V) 的電壓電平。

現(xiàn)在您已經(jīng)熟悉了 ECL 反相器/緩沖器,您應該能夠驗證圖 2 的電路是否實現(xiàn)了 a 和 b 的 OR 函數(shù)或 a 和 b 的 NOR 函數(shù),具體取決于正負輸出的方式被使用。

低電壓擺幅

低電壓擺幅正如您所看到的,ECL 門的邏輯高電平和低電平之間的電壓差遠小于CMOS 或 TTL 邏輯門的電壓差。這種低電壓差減少了從邏輯高電平轉(zhuǎn)換到邏輯低電平或反之亦然所需的時間。因此,ECL 邏輯可提供更高頻率的操作。

避免飽和

除了邏輯電平之間的低電壓差之外,還有另一種機制對 ECL 門的高速運行有顯著貢獻。訣竅是防止雙極晶體管進入飽和區(qū)。關(guān)閉飽和雙極晶體管需要去除或重新組合晶體管基極區(qū)中產(chǎn)生的一些載流子。

如果我們對飽和 BJT 的輸入應用從高到低的轉(zhuǎn)換,則晶體管輸出不會改變,直到基極中的電荷被移除。這會給用作開關(guān)的 BJT 的操作帶來額外的延遲,稱為存儲時間。經(jīng)過存儲時間后,晶體管脫離飽和狀態(tài),晶體管的輸出開始響應輸入。

如果選擇適當?shù)碾娮柚担珽CL 邏輯可防止晶體管進入飽和狀態(tài)。例如,在圖1中,選擇R1、R2和R3,使得Q1和Q2的集電極電壓不能小于約4.1V。基于上述討論,Q1和Q2的最大發(fā)射極電壓約為3.8V因此,這兩個晶體管的集電極-發(fā)射極電壓始終大于$$V_{C(min)}-V_{E(max)}$$=4.1 V-3.8 V=0.3。 V。這比集電極-發(fā)射極飽和電壓大,約為 0.2V。因此,Q1和Q2不能進入飽和區(qū)。

如上所述,ECL 通過正確選擇電阻值來避免存儲時間問題。由于存儲時間可能占其他邏輯系列中傳播延遲的很大一部分,因此有幾種其他方法可以減少這種不良影響。

正向參考 ECL

值得一提的是,舊的 ECL 系列使用負電源電壓,如圖 3 所示。這就是為什么圖 1 等使用正電源電壓的 ECL 門被稱為正參考 ECL 或 PECL(發(fā)音為“peckle”)。 ”)。

抗噪聲能力是早期 ECL 門使用負電源的主要原因。正如對 ECL 反相器/緩沖器的分析所示,ECL 門的輸出電壓取決于 $$V_{CC}$$ 的值。例如,邏輯高電平等于$$V_{CC}-V_{BE}$$,其中$$V_{BE}$$是發(fā)射極跟隨器的基極-發(fā)射極壓降。邏輯低電平為$$V_{CC}-V_{BE}-V_{gate}$$,其中$$V_{gate}$$是邏輯高電平和低電平之間的電壓差,由電阻器。因此,$$V_{CC}$$ 上的任何噪聲都會直接影響 ECL 門的輸出電壓。

抗噪聲能力是早期 ECL 門使用負電源的主要原因。正如對 ECL 反相器/緩沖器的分析所示,ECL 門的輸出電壓取決于 $$V_{CC}$$ 的值。例如,邏輯高電平等于$$V_{CC}-V_{BE}$$,其中$$V_{BE}$$是發(fā)射極跟隨器的基極-發(fā)射極壓降。邏輯低電平為$$V_{CC}-V_{BE}-V_{gate}$$,其中$$V_{gate}$$是邏輯高電平和低電平之間的電壓差,由電阻器。因此,$$V_{CC}$$ 上的任何噪聲都會直接影響 ECL 門的輸出電壓。通常,實現(xiàn)穩(wěn)定的低噪聲接地節(jié)點比穩(wěn)定的低噪聲電源電壓更容易。早期的 ECL 系列使用負電源,并使用接地作為柵極輸出電壓的參考;這帶來了更好的抗噪能力。然而,PECL 變得流行是因為它更容易與其他邏輯系列(例如 TTL)連接。

如果使用負電源,則需要在整個設計的基于 ECL 的部分分配干凈的接地。使用正參考 ECL 時,同樣的考慮因素也應適用于電源分配。例如,如果系統(tǒng)中同時使用 TTL 和 ECL,建議為兩個邏輯系列使用單獨的電源層,以便 TTL 開關(guān)瞬變不會影響 ECL 操作。

功耗

在圖 1 中,我們看到改變輸入的邏輯狀態(tài)會使電流流過 Q1 或 Q2。然而,應該注意的是,流過 Q1 和 Q2 的總電流對于邏輯高輸入和邏輯低輸入幾乎相同。因此,ECL 電路第一級的功耗幾乎恒定。

在電壓轉(zhuǎn)換期間,CMOS 邏輯門會引起電源電壓的瞬態(tài)干擾。 ECL 的一個主要優(yōu)點是輸入級(即 Q1 和 Q2)的電流控制行為不會像 CMOS 開關(guān)那樣引起干擾。

然而,這種噪聲性能是以消耗更多靜態(tài)功耗為代價實現(xiàn)的。請注意,CMOS 柵極僅在電壓轉(zhuǎn)換期間消耗功率,而 Q1 和 Q2 形成的差分對(見圖 1)幾乎總是從 $$\tfrac{4V}{1.3k \Omega} \approx 3mA$$ 汲取功率。 $V_{CC}$$。

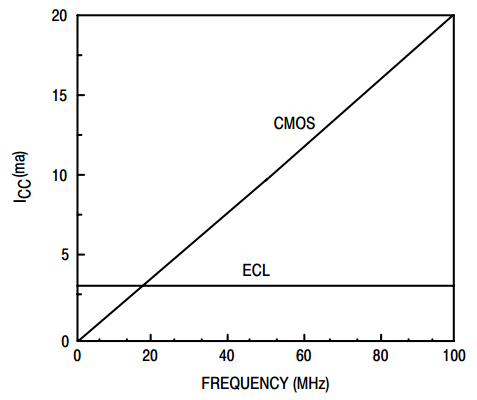

如果我們關(guān)注靜態(tài)功耗,ECL 是一個高功耗邏輯系列。然而,如果我們考慮動態(tài)功耗,ECL 可能比 CMOS 更高效,特別是當工作頻率增加時。如圖 4 所示。

低于 20 MHz 時,ECL 比 CMOS 消耗更多的電源電流,但當頻率超過該頻率時,ECL 會變得更加高效。這就是為什么 ECL 是高頻時鐘分配的有吸引力的解決方案。

最后要注意的是,射極跟隨器(見圖 1)必須提供大輸出電流來為負載電容充電,因此它們可能會導致電源電壓出現(xiàn)顯著的瞬態(tài)偏差。因此,在某些情況下,建議使用兩條單??獨的電源線:一根用于輸入級,一根用于射極跟隨器。這可以防止射極跟隨器產(chǎn)生的電源干擾污染ECL差分對。

版權(quán)與免責聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔此類作品侵權(quán)行為的直接責任及連帶責任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負版權(quán)等法律責任。

如涉及作品內(nèi)容、版權(quán)等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。