淺談低功耗概述及特性優(yōu)勢

出處:木頭東瓜 發(fā)布于:2011-09-01 22:58:22

概述

由于功耗敏感應(yīng)用大幅增加,加上功率預(yù)算日益緊張,低的系統(tǒng)功耗已成為越來越多應(yīng)用的需要。當(dāng)今,F(xiàn)PGA技術(shù)更多地用于低功耗設(shè)備,這使得降低系統(tǒng)功耗成為日益重要的挑戰(zhàn)。近年來,F(xiàn)PGA因為采用了能降低成本的先進(jìn)的工藝技術(shù),應(yīng)用也日益廣泛。但在成本降低的同時,功耗也因為高的晶體管漏電流而增加。不同的FPGA技術(shù)有顯著不同的功耗方式,這些差異對系統(tǒng)整體設(shè)計和功率預(yù)算有著深遠(yuǎn)的影響。Actel的超低功耗flash FPGA功耗,提供精選功率模式,且封裝尺寸小,在業(yè)界居于地位。

特性和優(yōu)勢

總系統(tǒng)功耗

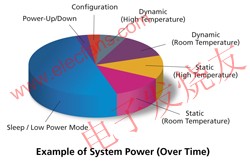

在評估不同F(xiàn)PGA技術(shù)的功耗時,需要考慮以下五種基本功耗元素:

靜態(tài)功耗

動態(tài)功耗

上電功耗 (或起動功耗)

配置功耗

睡眠模式 (或低功耗模式) 功耗

這些減少了一個終端系統(tǒng)的總功耗,而這反過來又有望降低我們對于化石燃料的依賴。由于可以將較低的功耗直接視為等同于所需電力的減少,因此使得上述目標(biāo)得以實現(xiàn)。而且,較少的電力消耗首先意味著產(chǎn)生電能所需的化石燃料的減少。相應(yīng)地,這將有助于減少對于我們所居住星球的大氣和氣候具有負(fù)面影響的溫室氣體。 總體系統(tǒng)功耗是五種功耗元素按時間比例的組合。

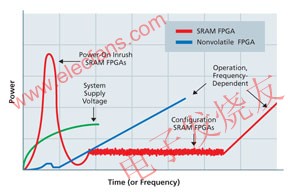

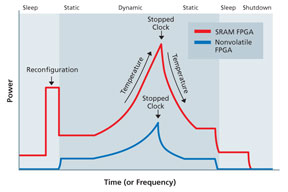

下面的對比圖表給出了基于SRAM的FPGA與基于 flash/反熔絲技術(shù)的非易失性FPGA的功耗比較,其中,左邊為上電功耗方式,右邊為不同運作模式的功耗。

功率方式與功耗

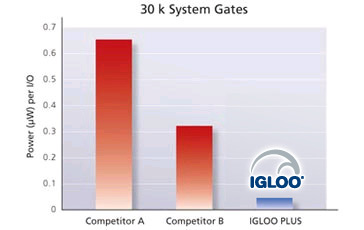

相比接近的低功耗競爭產(chǎn)品,采用Actel IGLOO器件能夠延長電池壽命達(dá)10倍,若采用Actel 的IGLOO PLUS器件,每I/O的功耗更低至接近低功耗競爭產(chǎn)品的16分之一。這是因為Actel的產(chǎn)品在系統(tǒng)運行的所有五個階段中具有出色的總體功率方式及更低的功耗。功耗一般分兩種:來自開關(guān)的動態(tài)功耗,和來自漏電的靜態(tài)功耗。而動態(tài)功耗又可分為電容充放電(包括網(wǎng)絡(luò)電容和輸入負(fù)載),還有當(dāng)P/N MOS 同時打開形成的瞬間短路電流。靜態(tài)功耗也可分為幾類:擴散區(qū)和襯底形成二極管的反偏電流(Idiode),另外一類是關(guān)斷晶體管中通過柵氧的電流(Isubthreshold)。芯片的漏電會隨溫度變化,所以當(dāng)芯片發(fā)熱時,靜態(tài)功耗指數(shù)上升。另外漏電流也會隨特征尺寸減少而增加。

下圖所示為每款器件的電池壽命和每I/O功耗的比較,有關(guān)數(shù)據(jù)是基于廠商的軟件功率分析工具。

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫電子市場網(wǎng)”的所有作品,版權(quán)均屬于維庫電子市場網(wǎng),轉(zhuǎn)載請必須注明維庫電子市場網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點或證實其內(nèi)容的真實性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個人從本網(wǎng)轉(zhuǎn)載時,必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問題,請在作品發(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- ARM技術(shù)架構(gòu)與應(yīng)用開發(fā)實踐指南2026/1/6 10:40:19

- 嵌入式實時操作系統(tǒng)(RTOS)選型與移植技術(shù)指南2025/12/31 10:42:31

- 工業(yè)嵌入式系統(tǒng):通信接口技術(shù)選型與抗干擾設(shè)計實踐2025/12/15 14:36:53

- 深入解析嵌入式 OPENAMP 框架:開啟異核通信新時代2025/7/22 16:27:29

- 一文快速了解OPENWRT基礎(chǔ)知識2025/7/14 16:59:04