通過(guò)最大限度地減少熱回路 PCB ESR 和 ESL 來(lái)優(yōu)化開(kāi)關(guān)電源布局

出處:維庫(kù)電子市場(chǎng)網(wǎng) 發(fā)布于:2024-10-22 16:48:43 | 450 次閱讀

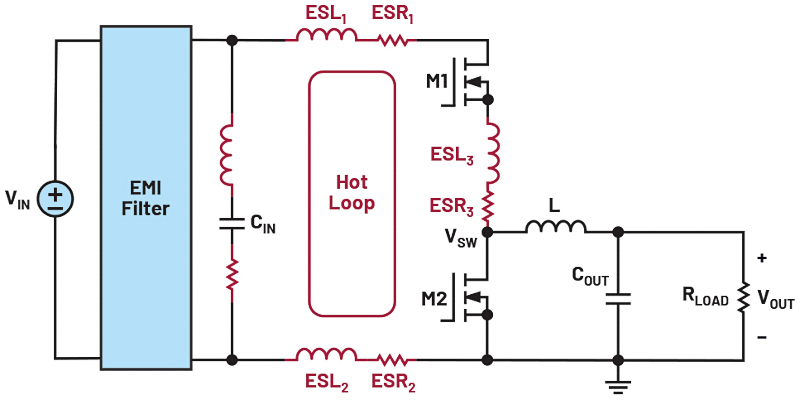

開(kāi)關(guān)模式電源轉(zhuǎn)換器的熱回路定義為由 HF 電容器和相鄰功率 FET 形成的關(guān)鍵高頻 (HF) 交流電流回路。它是功率級(jí) PCB 布局中最關(guān)鍵的部分,因?yàn)樗?dv/dt 和 di/dt 噪聲內(nèi)容。設(shè)計(jì)不佳的熱回路布局會(huì)受到高水平的 PCB 寄生參數(shù)的影響,包括 ESL、ESR 和等效并聯(lián)電容 (EPC),這些參數(shù)對(duì)電源轉(zhuǎn)換器的效率、開(kāi)關(guān)性能和 EMI 性能有重大影響。

圖 1 顯示了同步降壓 DC-DC 轉(zhuǎn)換器原理圖。熱回路由 MOSFET M1 和 M2 以及去耦電容器 C 形成在.M1 和 M2 的開(kāi)關(guān)動(dòng)作會(huì)導(dǎo)致 HF di/dt 和 dv/dt 噪聲。C在提供低阻抗路徑以繞過(guò) HF 噪聲內(nèi)容。然而,寄生阻抗(ESR、ESL)存在于元件封裝內(nèi)和熱回路 PCB 走線上。通過(guò) ESL 的高 di/dt 噪聲會(huì)導(dǎo)致 HF 振鈴,進(jìn)而導(dǎo)致 EMI。存儲(chǔ)在 ESL 中的能量耗散在 ESR 上,導(dǎo)致額外的功率損耗。因此,應(yīng)盡量減少熱回路 PCB ESR 和 ESL,以減少 HF 振鈴并提高效率。 精確提取熱回路 ESR 和 ESL 有助于預(yù)測(cè)開(kāi)關(guān)性能并改進(jìn)熱回路設(shè)計(jì)。元件的封裝和 PCB 走線都對(duì)總環(huán)路寄生參數(shù)有影響。這項(xiàng)工作主要集中在 PCB 布局設(shè)計(jì)上。有工具供用戶提取PCB寄生參數(shù),如Ansys Q3D、FastHenry/FastCap、StarRC等。Ansys Q3D 等商業(yè)工具可提供精確的仿真,但通常價(jià)格昂貴。FastHenry/FastCap 是一款基于部分元件等效電路 (PEEC) 數(shù)值建模1 的免費(fèi)工具,可以通過(guò)編程提供靈活的仿真,以探索不同的布局設(shè)計(jì),但需要額外的編碼。FastHenry/FastCap 中寄生參數(shù)提取的有效性和準(zhǔn)確性已得到驗(yàn)證,并與 Ansys Q3D 進(jìn)行了比較,結(jié)果一致2,3。在本文中,F(xiàn)astHenry 被用作提取 PCB ESR 和 ESL 的經(jīng)濟(jì)高效工具。

熱回路 PCB ESR 和 ESL 與去耦電容器位置的關(guān)系

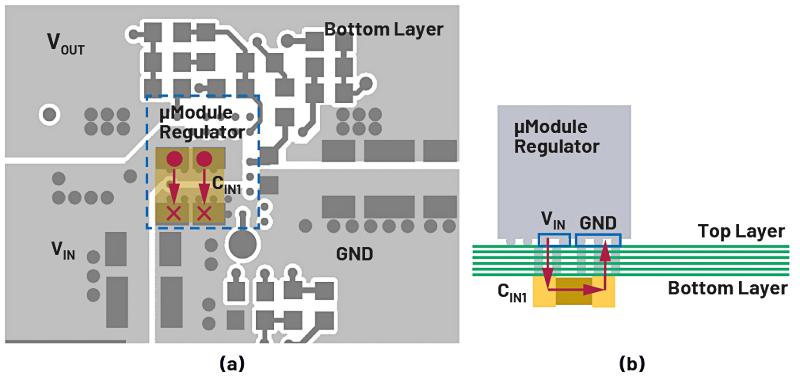

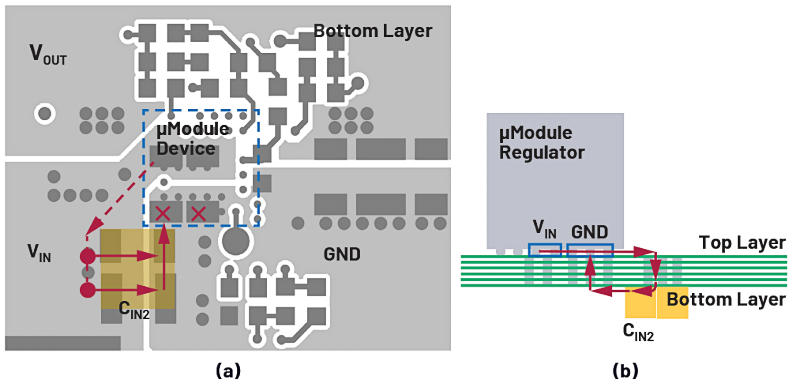

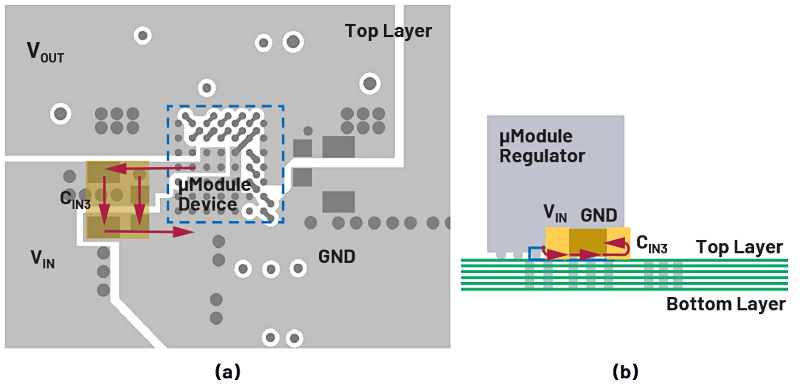

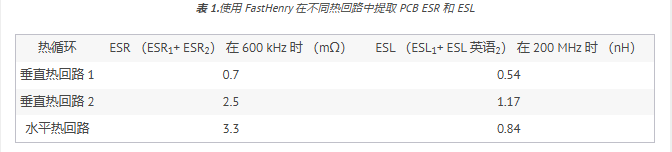

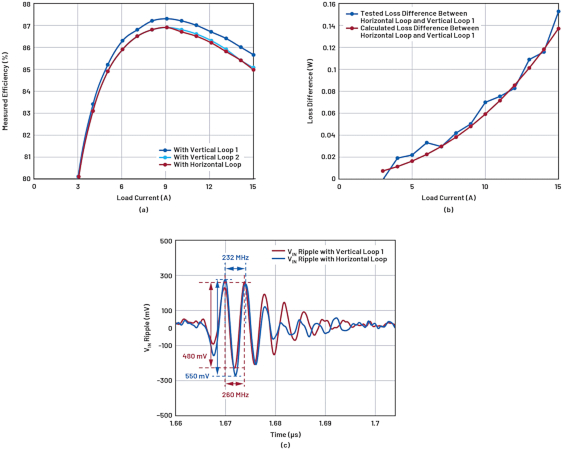

在本節(jié)中,C 的影響在位置基于 ADI 的 LTM4638 μModule? 穩(wěn)壓器演示板 DC2665A-B 進(jìn)行研究。LTM4638 是集成的 20 V在,15 A 降壓轉(zhuǎn)換器模塊,采用微型 6.25 mm × 6.25 mm × 5.02 mm BGA 封裝。它提供高功率密度、快速瞬態(tài)響應(yīng)和高效率。該模塊集成了一個(gè)小型 HF 陶瓷 C在內(nèi)部,雖然還不夠,但受模塊封裝尺寸的限制。圖 2 到圖 4 顯示了演示板上的三種不同的熱回路,并帶有額外的外部 C在.第一個(gè)是垂直熱回路 1(圖 2),其中 CIN1 系列放置在 μModule 穩(wěn)壓器正下方的底層。The ?Module V在GND BGA 引腳連接到 CIN1 系列直接通過(guò)過(guò)孔。這些連接在演示板上提供最短的熱回路路徑。第二個(gè)熱回路是垂直熱回路 2(圖 3),其中 CIN2仍位于底層,但移至 μModule 穩(wěn)壓器的側(cè)面區(qū)域。因此,與垂直熱回路 1 相比,熱回路中增加了額外的 PCB 走線,預(yù)計(jì) ESL 和 ESR 會(huì)更大。第三個(gè)熱回路選項(xiàng)是水平熱回路(圖 4),其中 CIN3放置在靠近 μModule 穩(wěn)壓器的頂層。The ?Module V在GND 引腳連接到 CIN3穿過(guò)頂層銅,不穿過(guò)過(guò)孔。盡管如此,V在頂層的銅寬受另一個(gè)引腳的限制,導(dǎo)致與垂直熱回路 1 相比,環(huán)路阻抗增加。表 1 比較了 FastHenry 提取的熱回路的 PCB ESR 和 ESL。正如預(yù)期的那樣,垂直熱回路 1 具有最低的 PCB ESR 和 ESL。 為了實(shí)驗(yàn)驗(yàn)證不同熱回路中的 ESR 和 ESL,演示板效率和 V在測(cè)試了 12 V 至 1 V CCM 操作時(shí)的交流紋波。理論上,較低的 ESR 會(huì)導(dǎo)致更高的效率,而較小的 ESL 會(huì)導(dǎo)致較高的 V西 南部振鈴頻率和較低的 VIN 紋波幅度。圖 5a 顯示了測(cè)得的效率。垂直熱回路 1 提供對(duì)應(yīng)于最低 ESR 的最高效率。水平熱回路和垂直熱回路 1 之間的損耗差也是根據(jù)提取的 ESR 計(jì)算的,這與圖 5b 所示的測(cè)試結(jié)果一致。V 形在圖 5c 中的 HF 紋波波形是在 C 之間進(jìn)行測(cè)試的在.水平熱回路具有更高的 V在紋波幅度和較低的振鈴頻率,從而驗(yàn)證了與垂直熱回路 1 相比更高的環(huán)路 ESL。此外,由于環(huán)路 ESR 較高,水平熱回路中的 VIN 紋波比垂直熱回路 1 中的 VIN 紋波衰減得更快。此外,較低的 VIN 紋波可降低 EMI 并允許更小的 EMI 濾波器尺寸。

圖 2.垂直熱回路 1:(a) 頂視圖和 (b) 側(cè)視圖。圖片由 Bodo's Power Systems 提供

圖 3. 垂直熱回路 2:(a) 頂視圖和 (b) 側(cè)視圖。圖片由 Bodo's Power Systems 提供

熱回路 PCB ESR 和 ESL 與 MOSFET 的尺寸和位置

對(duì)于分立設(shè)計(jì),功率 FET 的布局和封裝尺寸也會(huì)對(duì)熱回路 ESR 和 ESL 產(chǎn)生重大影響。本節(jié)對(duì)具有功率 FET M1 和 M2 以及去耦電容器 CIN 的典型半橋熱回路進(jìn)行建模和研究。如圖 6 所示,比較了流行的功率 FET 封裝尺寸和放置位置。表 2 顯示了每種情況下提取的 ESR 和 ESL。

情況 (a) 至 (c) 介紹了三種常用的功率 FET 布局,采用 5 mm × 6 mm MOSFET。熱回路的物理長(zhǎng)度決定了寄生阻抗。因此,情況 (b) 中的 90° 形狀放置和情況 (c) 中的 180° 形狀器件放置都會(huì)導(dǎo)致 ESR 降低 60% 和 ESL 降低 80%,因?yàn)榕c情況 (a) 相比,環(huán)路路徑更短。由于 90° 形狀放置顯示出好處,因此根據(jù)案例 (b) 研究了更多案例,以進(jìn)一步降低環(huán)路 ESR 和 ESL。在情況 (d) 中,一個(gè) 5 mm × 6 mm MOSFET 被兩個(gè)并聯(lián)的 3.3 mm × 3.3 mm MOSFET 取代。由于更小的 MOSFET 尺寸,環(huán)路長(zhǎng)度進(jìn)一步縮短,從而使環(huán)路阻抗降低 7%。在情況 (e) 中,當(dāng)在熱回路層下放置接地層時(shí),與情況 (d) 相比,熱回路 ESR 和 ESL 進(jìn)一步降低了 2%。原因是在接地層上產(chǎn)生渦流,感應(yīng)出相反的磁場(chǎng),等效地降低了環(huán)路阻抗。在情況 (f) 中,另一個(gè)熱回路層被構(gòu)造為底層。如果兩個(gè)并聯(lián)的 MOSFET 對(duì)稱地放置在頂層和底層,并通過(guò)過(guò)孔連接,則由于并聯(lián)阻抗,熱回路 PCB ESR 和 ESL 的降低更加明顯。因此,在頂層和底層具有對(duì)稱 90° 形狀或 180° 形狀布局的較小尺寸器件可實(shí)現(xiàn)最低的 PCB ESR 和 ESL。 表 1.使用 FastHenry 在不同熱回路中提取 PCB ESR 和 ESL

垂直熱回路 10.70.54

垂直熱回路 22.51.17 水平熱回路3.30.84

版權(quán)與免責(zé)聲明

凡本網(wǎng)注明“出處:維庫(kù)電子市場(chǎng)網(wǎng)”的所有作品,版權(quán)均屬于維庫(kù)電子市場(chǎng)網(wǎng),轉(zhuǎn)載請(qǐng)必須注明維庫(kù)電子市場(chǎng)網(wǎng),http://hbjingang.com,違反者本網(wǎng)將追究相關(guān)法律責(zé)任。

本網(wǎng)轉(zhuǎn)載并注明自其它出處的作品,目的在于傳遞更多信息,并不代表本網(wǎng)贊同其觀點(diǎn)或證實(shí)其內(nèi)容的真實(shí)性,不承擔(dān)此類作品侵權(quán)行為的直接責(zé)任及連帶責(zé)任。其他媒體、網(wǎng)站或個(gè)人從本網(wǎng)轉(zhuǎn)載時(shí),必須保留本網(wǎng)注明的作品出處,并自負(fù)版權(quán)等法律責(zé)任。

如涉及作品內(nèi)容、版權(quán)等問(wèn)題,請(qǐng)?jiān)谧髌钒l(fā)表之日起一周內(nèi)與本網(wǎng)聯(lián)系,否則視為放棄相關(guān)權(quán)利。

- LM317:高效構(gòu)建電壓源及電流源電路方案1

- 如何使用多相轉(zhuǎn)換器平衡電流2

- LTC4365 如何實(shí)現(xiàn)敏感電路過(guò)壓與反接保護(hù)3

- MOS 管邏輯電路五種門電路特性4

- 點(diǎn)動(dòng)正轉(zhuǎn)控制電路簡(jiǎn)介5

- 單鍵開(kāi)關(guān)機(jī)電路與輕觸開(kāi)關(guān)的創(chuàng)新設(shè)計(jì)解析6

- 二極管的恒壓降模型7

- MC34063電路計(jì)算公式及應(yīng)用講解8

- 3.3V - 1.8V 電平雙向轉(zhuǎn)換:多場(chǎng)景配置及獨(dú)特優(yōu)勢(shì)剖析9

- 液晶電視機(jī)電路結(jié)構(gòu)的關(guān)鍵要點(diǎn)10

- XR2206函數(shù)發(fā)生器

- MC34063電路計(jì)算公式及應(yīng)用講解

- 二極管的恒壓降模型

- 點(diǎn)動(dòng)正轉(zhuǎn)控制電路簡(jiǎn)介

- 如何使用多相轉(zhuǎn)換器平衡電流

- 液晶電視機(jī)電路結(jié)構(gòu)的關(guān)鍵要點(diǎn)

- LTC4365 如何實(shí)現(xiàn)敏感電路過(guò)壓與反接保護(hù)

- 單鍵開(kāi)關(guān)機(jī)電路與輕觸開(kāi)關(guān)的創(chuàng)新設(shè)計(jì)解析

- MOS 管邏輯電路五種門電路特性

- LM317:高效構(gòu)建電壓源及電流源電路方案