TDK - 面向緊湊型高性能FPGA、SoC和ASIC的次世代垂直供電解決方案

隨著人工智能 (AI) 和邊緣應(yīng)用日趨完善和復(fù)雜,對(duì)處理器、ASIC和FPGA/SoC的計(jì)算能力和電源要求也水漲船高。因?yàn)檫@些設(shè)備須在更狹小的空間內(nèi)高效運(yùn)行,同時(shí)保持高性能。垂直...

分類:電源技術(shù) 時(shí)間:2025-02-27 閱讀:1034 關(guān)鍵詞:FPGASoCASIC

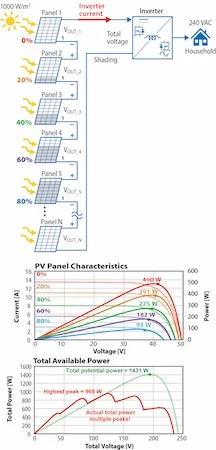

光伏優(yōu)化器使用 eGaN FET 和專用 ASIC 控制器

第一種配置是微型逆變器,它為安裝中的每個(gè)面板使用逆變器,確保每個(gè)面板都能發(fā)揮其全部能源潛力。第二個(gè)是串式逆變器,它將多個(gè)面板連接在一起并向中央逆變器供電。然而,...

分類:元器件應(yīng)用 時(shí)間:2024-11-27 閱讀:781 關(guān)鍵詞: ASIC 控制器

SoC芯片(系統(tǒng)級(jí)芯片,System on Chip)和ASIC芯片(特定應(yīng)用集成電路,Application-Specific Integrated Circuit)都是現(xiàn)代電子設(shè)備中廣泛使用的集成電路(IC),但它們?cè)诠δ堋⒃O(shè)計(jì)和應(yīng)用上有所不同。下面是兩者的...

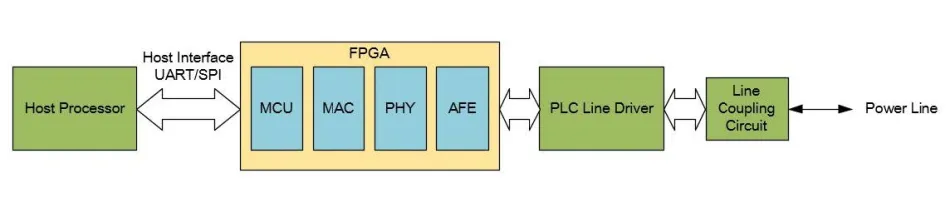

用于完善智能電表設(shè)計(jì)的 FPGA 到 ASIC 案例研究

許多嵌入式系統(tǒng)設(shè)計(jì)首先使用 FPGA 來(lái)實(shí)現(xiàn)。這可能是為了更快地進(jìn)行原型設(shè)計(jì)或提供軟件開(kāi)發(fā)平臺(tái)。有時(shí),生產(chǎn)開(kāi)始后,F(xiàn)PGA 仍保留在設(shè)計(jì)中。但通常情況下,計(jì)劃是將 FPGA(或...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時(shí)間:2023-11-10 閱讀:1487 關(guān)鍵詞:FPGA

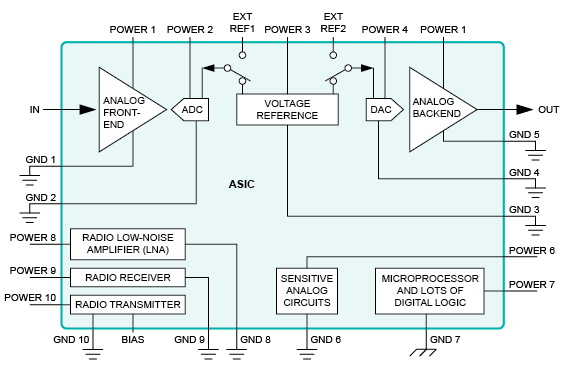

針對(duì)噪聲模擬設(shè)計(jì)的 ASIC 修復(fù)

噪聲是混合信號(hào) ASIC 中的一個(gè)常見(jiàn)問(wèn)題,會(huì)降低性能并危及產(chǎn)品的完成度。本應(yīng)用筆記提供了添加外部電路的提示和技巧,使許多 ASIC 可用于原型設(shè)計(jì)或作為最終產(chǎn)品進(jìn)行交付。...

FPGA要取代ASIC了,這是FPGA廠商喊了十多年的口號(hào)。可是,F(xiàn)PGA地盤(pán)占了不少,ASIC也依舊玩得愉快。這兩位仁兄到底有啥不一樣呢? 一、身份證 FPGA(Field-Programma...

分類:其它 時(shí)間:2019-12-11 閱讀:726 關(guān)鍵詞:FPGA ,ASIC

MediaTek ASIC服務(wù)推出硅驗(yàn)證的7nm制程112G遠(yuǎn)程SerDes IP

MediaTek憑借在數(shù)據(jù)中心、AI計(jì)算和云基礎(chǔ)架構(gòu)領(lǐng)域的SerDes產(chǎn)品組合引領(lǐng)行業(yè)。 2019年11月11日 - MediaTek今日宣布,其ASIC服務(wù)將擴(kuò)展至112G遠(yuǎn)程(LR)SerDes IP芯片。MediaTek的112G 遠(yuǎn)程 SerDes采用經(jīng)過(guò)硅驗(yàn)證...

時(shí)間:2019-11-12 閱讀:1025 關(guān)鍵詞:7nm制程,MediaTek ASIC

基于DSP+FPGA+ASIC的實(shí)時(shí)圖像處理架構(gòu)設(shè)計(jì)

隨著紅外焦平面陣列技術(shù)的快速發(fā)展,紅外成像系統(tǒng)實(shí)現(xiàn)了高幀頻、高分辨率、高可靠性及微型化,在目標(biāo)跟蹤、智能交通監(jiān)控中得到了越來(lái)越多的應(yīng)用,并向更加廣泛的軍事及民用...

分類:單片機(jī)與DSP 時(shí)間:2018-09-05 閱讀:699 關(guān)鍵詞:基于DSP+FPGA+ASIC的實(shí)時(shí)圖像處理架構(gòu)設(shè)計(jì)DSP+FPGA+ASIC

FPGA該如何應(yīng)對(duì)ASIC的大爆發(fā)?

有人認(rèn)為,除了人才短缺、開(kāi)發(fā)難度較大,相比未來(lái)的批量化量產(chǎn)的ASIC芯片,F(xiàn)PGA在成本、性能、功耗方面仍有很多不足。這是否意味著,在ASIC大爆發(fā)之際,F(xiàn)PGA將淪為其“過(guò)渡...

時(shí)間:2018-08-30 閱讀:517 關(guān)鍵詞:FPGA,ASIC

適用于 FPGA、GPU 和 ASIC 系統(tǒng)的電源管理

在 FPGA、GPU 或 ASIC 控制的系統(tǒng)板上,僅有為數(shù)不多的幾種電源管理相關(guān)的設(shè)計(jì)挑戰(zhàn),但是由于需要反復(fù)調(diào)試,所以這類挑戰(zhàn)可能使系統(tǒng)的推出時(shí)間嚴(yán)重滯后。不過(guò),如果特定設(shè)...

分類:電源技術(shù) 時(shí)間:2018-08-09 閱讀:868 關(guān)鍵詞:FPGA,GPU,ASIC,電源管理

汽車(chē)電子EMC汽車(chē)系統(tǒng)ASIC、ASSP和電磁兼容性(EMC)設(shè)計(jì)

現(xiàn)代汽車(chē)中的電子設(shè)備不斷增多,因而越來(lái)越需要采用良好的設(shè)計(jì),以滿足主要的電磁兼容性標(biāo)準(zhǔn)的要求。同時(shí),越來(lái)越高的集成度也讓汽車(chē)設(shè)計(jì)師們急需系統(tǒng)芯片專用集成電路和專用標(biāo)準(zhǔn)產(chǎn)品解決方案,它們可以替換多個(gè)分立...

分類:汽車(chē)電子/智能駕駛 時(shí)間:2018-08-09 閱讀:634 關(guān)鍵詞:汽車(chē)電子,EMC,電磁兼容性

在現(xiàn)代集成電路設(shè)計(jì)中,隨著集成度的不斷提升,常常會(huì)遇到數(shù)據(jù)緩存與不同時(shí)鐘域之間數(shù)據(jù)傳遞的問(wèn)題,在不同系統(tǒng)間如不能設(shè)計(jì)出有效的接口單元,將會(huì)產(chǎn)生數(shù)據(jù)傳輸過(guò)程中的復(fù)寫(xiě)、丟失和無(wú)效數(shù)據(jù)的讀入等錯(cuò)誤,同時(shí)亞穩(wěn)...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時(shí)間:2018-07-24 閱讀:261 關(guān)鍵詞:一種基于ASIC的高速異步FIFO設(shè)計(jì)ASIC,FIFO設(shè)計(jì)

Xilinx新一代UltraScale架構(gòu)成為ASIC或SOC原型驗(yàn)證的選擇

近年來(lái),ASIC設(shè)計(jì)規(guī)模的增大帶來(lái)了前所未有的芯片原型驗(yàn)證問(wèn)題,單顆大容量的FPGA通常已不足以容下千萬(wàn)門(mén)級(jí)、甚至上億門(mén)級(jí)的邏輯設(shè)計(jì)。現(xiàn)今,將整個(gè)驗(yàn)證設(shè)計(jì)分割到多個(gè)采用...

時(shí)間:2018-07-03 閱讀:1539 關(guān)鍵詞:Xilinx新一代UltraScale架構(gòu)成為ASIC或SOC原型驗(yàn)證的極佳選擇 芯片,ASIC

FPGA和ASIC之間界限正在模糊,F(xiàn)PGA為未來(lái)的ASIC提供設(shè)計(jì)架構(gòu)

與以前的自我相比,現(xiàn)在的FPGA不再僅僅是查找表(LUT)和寄存器的集合,而是已經(jīng)遠(yuǎn)遠(yuǎn)超出了現(xiàn)在的體系結(jié)構(gòu)的探索,為未來(lái)的ASIC提供設(shè)計(jì)架構(gòu)。該系列器件現(xiàn)在包括從基本的可編程邏輯一直到復(fù)雜的SoC。在各種應(yīng)用領(lǐng)域...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時(shí)間:2018-06-22 閱讀:314 關(guān)鍵詞:fpga,asic,可編程邏輯

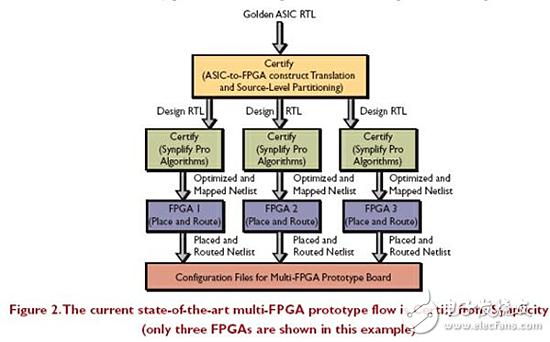

利用FPGA開(kāi)發(fā)板進(jìn)行ASIC原型開(kāi)發(fā)的技巧

ASIC設(shè)計(jì)在尺寸和復(fù)雜性上不斷增加,現(xiàn)代FPGA的容量和性能的新進(jìn)展意味著這些設(shè)計(jì)中的2/3能夠使用單個(gè)FPGA進(jìn)行建模。然而,這些設(shè)計(jì)中仍然保留有1/3(那就是說(shuō),所有ASIC設(shè)...

分類:模擬技術(shù) 時(shí)間:2017-11-25 閱讀:1068 關(guān)鍵詞:asic,fpga

ASIC設(shè)計(jì)中不可忽視的幾大問(wèn)題

時(shí)間:2017-05-15 閱讀:0

在 FPGA、GPU 或 ASIC 控制的系統(tǒng)板上,僅有為數(shù)不多的幾種電源管理相關(guān)的設(shè)計(jì)挑戰(zhàn),但是由于需要反復(fù)調(diào)試,所以這類挑戰(zhàn)可能使系統(tǒng)的推出時(shí)間嚴(yán)重滯后。不過(guò),如果特定設(shè)...

分類:電源技術(shù) 時(shí)間:2017-05-09 閱讀:1017 關(guān)鍵詞:適用于FPGA、GPU和ASIC系統(tǒng)的電源管理

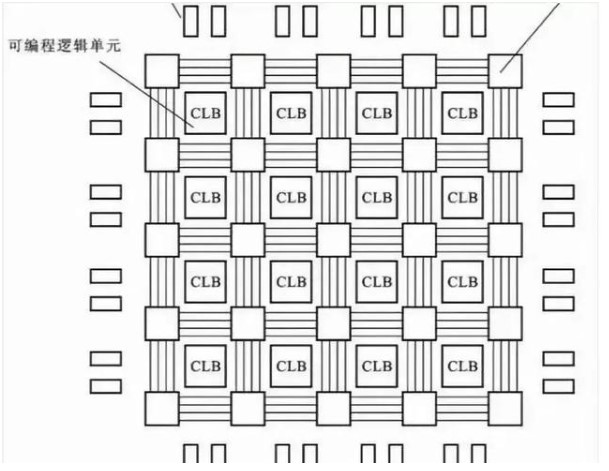

什么是FPGA,ASIC,如何設(shè)計(jì)一個(gè)適用于它們的供電系統(tǒng)

什么是FPGA? FPGA(Field-Programmable Gate Array),即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC...

時(shí)間:2017-05-08 閱讀:2447 關(guān)鍵詞:fpga,asic,電源

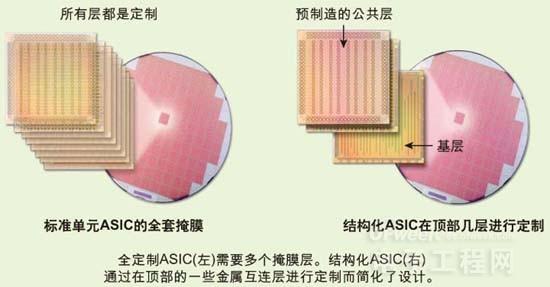

結(jié)合FPGA與結(jié)構(gòu)化ASIC進(jìn)行設(shè)計(jì)

由于結(jié)構(gòu)化ASIC具有單位成本低、功耗低、性能高和轉(zhuǎn)換快(fast turnaound)等特點(diǎn),越來(lái)越多的先進(jìn)系統(tǒng)設(shè)計(jì)工程師正在考慮予以采用。在結(jié)構(gòu)化ASIC中,像通用邏輯門(mén)、存儲(chǔ)器、...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時(shí)間:2015-12-08 閱讀:26671 關(guān)鍵詞:FPGAASIC邏輯設(shè)計(jì)

演示ASIC IP性能與質(zhì)量需要有FPGA中立的設(shè)計(jì)流程

設(shè)計(jì)新系統(tǒng)級(jí)芯片(SoC)產(chǎn)品的公司都面臨成本和效率壓力,以及實(shí)現(xiàn)更高投資回報(bào)的持續(xù)市場(chǎng)壓力,從而導(dǎo)致了工程團(tuán)隊(duì)縮編、設(shè)計(jì)工具預(yù)算降低以及新產(chǎn)品上市時(shí)間規(guī)劃縮短。...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時(shí)間:2015-03-02 閱讀:2155 關(guān)鍵詞:演示ASIC IP性能與質(zhì)量需要有FPGA中立的設(shè)計(jì)流程IP性能FPGA

- 編碼器的工作原理及作用1

- 超強(qiáng)整理!PCB設(shè)計(jì)之電流與線寬的關(guān)系2

- 三星(SAMSUNG)貼片電容規(guī)格對(duì)照表3

- 電腦藍(lán)屏代碼大全4

- 國(guó)標(biāo)委發(fā)布《電動(dòng)汽車(chē)安全要求第3部分:人員觸電防護(hù)》第1號(hào)修改單5

- 通俗易懂談上拉電阻與下拉電阻6

- 繼電器的工作原理以及驅(qū)動(dòng)電路7

- 電容單位8

- 跟我學(xué)51單片機(jī)(三):?jiǎn)纹瑱C(jī)串口通信實(shí)例9

- 一種三極管開(kāi)關(guān)電路設(shè)計(jì)10

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號(hào)完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車(chē)電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號(hào)鏈中的濾波與功耗管理