Achronix - 在FPGA設(shè)計中如何充分利用NoC資源去支撐創(chuàng)新應(yīng)用設(shè)計

日益增長的數(shù)據(jù)加速需求對硬件平臺提出了越來越高的要求,F(xiàn)PGA作為一種可編程可定制化的高性能硬件發(fā)揮著越來越重要的作用。近年來,高端FPGA芯片采用了越來越多的Hard IP...

時間:2021-01-29 閱讀:481 關(guān)鍵詞:Achronix - 在FPGA設(shè)計中如何充分利用NoC資源去支撐創(chuàng)新應(yīng)用設(shè)計FPGA設(shè)計

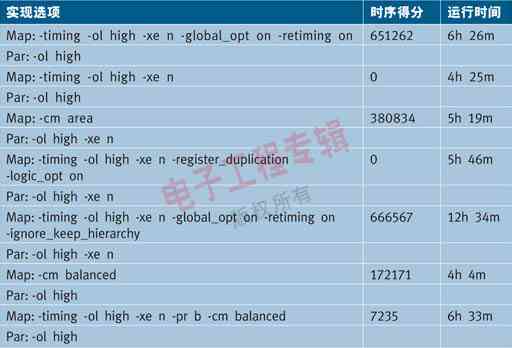

1.面積與速度的平衡與互換 這里的面積指一個設(shè)計消耗FPGA/CPLD的邏輯資源的數(shù)量,對于FPGA可以用消耗的FF(觸發(fā)器)和LUT(查找表)來衡量,更一般的衡量方式可以用設(shè)計所占的等價邏輯門數(shù)。 速度指設(shè)計在...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時間:2019-11-04 閱讀:780 關(guān)鍵詞:FPGA設(shè)計

FPGA設(shè)計100條經(jīng)典問答,快看看有沒有你需要的!

1 問:可否解釋下 FPGA 時序約束設(shè)置方法,目前在做一個項目,功能仿真正確,但想進(jìn)一步優(yōu)化設(shè)計,采用怎樣的時序約束才能達(dá)到目標(biāo)呢? 答: 優(yōu)化代碼,可以從代碼風(fēng)格的角度出發(fā),這就涉及到對整個系統(tǒng)的...

分類:其它 時間:2019-05-06 閱讀:2506 關(guān)鍵詞:FPGA設(shè)計100條經(jīng)典問答,快看看有沒有你需要的!FPGA設(shè)計

FPGA的用處比我們平時想象的用處更廣泛,原因在于其中集成的模塊種類更多,而不僅僅是原來的簡單邏輯單元(LE)。 早期的FPGA相對比較簡單,所有的功能單元僅僅由管腳、內(nèi)部buffer、LE、RAM構(gòu)建而成,LE由LUT(...

分類:模擬技術(shù) 時間:2018-09-07 閱讀:1044 關(guān)鍵詞:FPGA設(shè)計需要注意哪些要點FPGA設(shè)計

采用編譯增強(qiáng)技術(shù),提高高密度FPGA設(shè)計工作效率

現(xiàn)場可編程門陣列(FPGA)體系創(chuàng)新以及向90nm工藝技術(shù)的過渡顯著提高了FPGA的密度和性能。FPGA設(shè)計人員不僅需要更高的邏輯密度和更快的性能表現(xiàn),還要求具有嵌入式處理器、數(shù)字信號處理(DSP)模塊以及其他硬件IP結(jié)構(gòu)等...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時間:2018-08-01 閱讀:434 關(guān)鍵詞:分區(qū),編譯,設(shè)計器件,EDA

物聯(lián)網(wǎng)、人工智能、大數(shù)據(jù)等新興技術(shù)的推動,集成電路技術(shù)和計算機(jī)技術(shù)得到蓬勃發(fā)展。電子產(chǎn)品設(shè)計系統(tǒng)日趨數(shù)字化、復(fù)雜化和大規(guī)模集成化,各種電子系統(tǒng)的設(shè)計軟件應(yīng)運而生。在這些專業(yè)化軟件中,EDA(Electronic De...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時間:2018-07-26 閱讀:716 關(guān)鍵詞:EDA技術(shù),FPGA,設(shè)計

EDA技術(shù)與FPGA設(shè)計應(yīng)用詳解

摘 要:eda技術(shù)是現(xiàn)代電子設(shè)計技術(shù)的核心,它在現(xiàn)代集成電路設(shè)計中占據(jù)重要地位。隨著深亞微米與超深亞微米技術(shù)的迅速發(fā)展,fpga設(shè)計越來越多地采用基于vhdl的設(shè)計方法及先進(jìn)的eda工具。本文詳細(xì)闡述了eda技術(shù)與fpga...

分類:EDA/PLD/PLC 時間:2017-10-17 閱讀:2049 關(guān)鍵詞:EDA,FPGA

FPGA工程師不得不知的FPGA設(shè)計經(jīng)驗

這里談?wù)勔恍┙?jīng)驗和大家分享,希望能對IC設(shè)計的新手有一定的幫助,能使得他們能少走一些彎路! 在IC工業(yè)中有許多不同的領(lǐng)域,IC設(shè)計者的特征也會有些不同。在A領(lǐng)域的一個好的IC設(shè)計者也許會花很長時間去熟悉B領(lǐng)域...

時間:2017-09-08 閱讀:1560 關(guān)鍵詞:FPGA

十年開發(fā)經(jīng)驗工程師談FPGA設(shè)計技巧

從大學(xué)時代第一次接觸FPGA至今已有10多年的時間,至今記得當(dāng)初第一次在EDA實驗平臺上完成數(shù)字秒表、搶答器、密碼鎖等實驗時那個興奮勁。當(dāng)時由于沒有接觸到HDL硬件描述語言,設(shè)計都是在MAX+plus II原理圖環(huán)境下用74...

時間:2017-08-23 閱讀:1413 關(guān)鍵詞:十年開發(fā)經(jīng)驗工程師談FPGA設(shè)計技巧FPGA設(shè)計

集成電路技術(shù)和計算機(jī)技術(shù)的蓬勃發(fā)展。讓電子產(chǎn)品設(shè)計有了更好的應(yīng)用市場。實現(xiàn)方法也有了更多的選擇。傳統(tǒng)電子產(chǎn)品設(shè)計方案是一種基于電路板的設(shè)計方法。該方法需要選用大量的固定功能器件.然后通過這些器件的配合...

分類:EDA/PLD/PLC 時間:2017-08-02 閱讀:1388 關(guān)鍵詞:EDA,FPGA

這里我談?wù)勎业囊恍┙?jīng)驗和大家分享,希望能對IC設(shè)計的新手有一定的幫助,能使得他們能少走一些彎路! 在IC工業(yè)中有許多不同的領(lǐng)域,IC設(shè)計者的特征也會有些不同。在A領(lǐng)域的一個好的IC設(shè)計者也許會花很長時間去...

時間:2017-04-19 閱讀:633 關(guān)鍵詞:牛人的FPGA設(shè)計經(jīng)驗分享

1、不建議使用組合邏輯時鐘或門控時鐘。組合邏輯和門控時鐘很容易產(chǎn)生毛刺,用組合邏輯的輸出作為時鐘很容易使系統(tǒng)產(chǎn)生誤動作。2、不建議使用行波時鐘。行波記數(shù)器雖然原理簡單,設(shè)計方便,但級連時鐘(行波時鐘)最...

時間:2016-12-21 閱讀:680 關(guān)鍵詞:說一說FPGA設(shè)計中不建議使用的電路

掌握FPGA設(shè)計三大黃金法則 讓你設(shè)計更輕松!

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內(nèi)部包括 可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內(nèi)部連線(Interconnect)三個部分。 現(xiàn)場可編程...

時間:2016-12-09 閱讀:689 關(guān)鍵詞:掌握FPGA設(shè)計三大黃金法則 讓你設(shè)計更輕松!

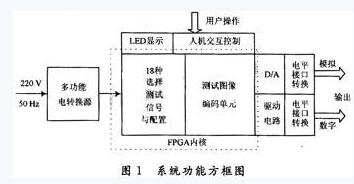

數(shù)字電視信號發(fā)生器原理及設(shè)計-FPGA設(shè)計篇

如何選擇自己理想的數(shù)字電視產(chǎn)品,也成了消費者關(guān)心的問題,評價、測試電視系統(tǒng)與設(shè)備運行的質(zhì)量狀況成為廣播電視行業(yè)所關(guān)注的熱點。 而數(shù)字電視信號發(fā)生器能提供可視的...

時間:2016-07-14 閱讀:1734 關(guān)鍵詞:數(shù)字電視信號發(fā)生器原理及設(shè)計-FPGA設(shè)計篇

從大學(xué)時代次接觸FPGA至今已有10多年的時間。至今記得當(dāng)初次在EDA實驗平臺上完成數(shù)字秒表,搶答器,密碼鎖等實驗時,那個興奮勁。當(dāng)時由于沒有接觸到HDL硬件描述語言,設(shè)計...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時間:2015-12-18 閱讀:31823 關(guān)鍵詞:FPGA設(shè)計資深工程師精華

隨著道路上汽車數(shù)量的增加,我們需要更多的技術(shù)來進(jìn)一步減少交通事故。過去幾年,基于雷達(dá)和攝像機(jī)的新系統(tǒng)功能的出現(xiàn)使駕駛更加安全。很多輔助駕駛系統(tǒng)(ADAS)應(yīng)用,如自...

分類:汽車電子/智能駕駛 時間:2014-08-27 閱讀:1331 關(guān)鍵詞:通過FPGA設(shè)計安全的高級輔助駕駛系統(tǒng)輔助駕駛系統(tǒng) 車輛控制 圖像處理 FPGA

當(dāng)你的FPGA設(shè)計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現(xiàn)工具來優(yōu)化設(shè)計從而滿足時序要求,也需要設(shè)計者具有明確目標(biāo)和診斷/隔離時序問題的能力。設(shè)計者現(xiàn)在有一些小技巧和幫助來...

分類:EDA/PLD/PLC 時間:2014-08-08 閱讀:1190 關(guān)鍵詞:在FPGA設(shè)計中,時序就是全部FPGA時序RTL

1 引言 基于FPGA的數(shù)字系統(tǒng)設(shè)計中大都推薦采用同步時序的設(shè)計,也就是單時鐘系統(tǒng)。但是實際的工程中,純粹單時鐘系統(tǒng)設(shè)計的情況很少,特別是設(shè)計模塊與外圍芯片的通信中...

分類:EDA/PLD/PLC 時間:2012-02-21 閱讀:6026 關(guān)鍵詞:基于FPGA設(shè)計跨時鐘域的同步策略

隨著FPGA密度的增加,系統(tǒng)設(shè)計人員能夠開發(fā)規(guī)模更大、更復(fù)雜的設(shè)計,從而將密度優(yōu)勢發(fā)揮到。這些大規(guī)模設(shè)計基于這樣的設(shè)計需求——需要在無線通道卡或者線路卡等現(xiàn)有應(yīng)用中...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時間:2011-11-30 閱讀:2843 關(guān)鍵詞:FPGA設(shè)計效能提高方法FPGA

耗費數(shù)月精力做出的設(shè)計卻無法滿足時序要求,這確實非常令人傷心。然而,試圖正確地對設(shè)計進(jìn)行約束以保證滿足時序要求的過程幾乎同樣令人費神。找到并確定時序約束本身通常...

分類:其它 時間:2011-09-04 閱讀:1898 關(guān)鍵詞:FPGAFPGA設(shè)計