VGG介紹卷積神經(jīng)網(wǎng)絡(luò)的模型結(jié)構(gòu)

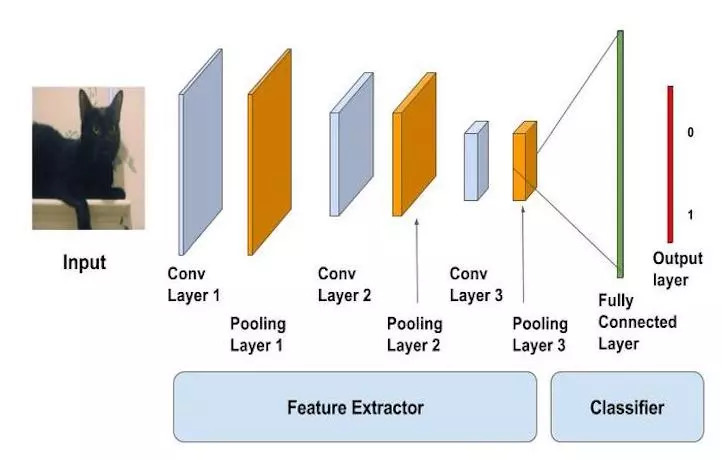

VGG(Visual Geometry Group)是一種著名的卷積神經(jīng)網(wǎng)絡(luò)(CNN)架構(gòu),最初由牛津大學(xué)的一個研究小組在2014年的ImageNet挑戰(zhàn)賽中提出。VGG模型以其簡單而深的網(wǎng)絡(luò)結(jié)構(gòu)而聞名,特別是在圖像分類任務(wù)中取得了優(yōu)異的成績...

分類:其它 時間:2024-08-15 閱讀:593 關(guān)鍵詞:神經(jīng)網(wǎng)絡(luò)

卷積的意義廣泛且深遠(yuǎn),尤其在以下幾個領(lǐng)域中表現(xiàn)得尤為重要: 1. 信號處理 在信號處理中,卷積用于對信號進(jìn)行濾波、平滑、去噪或增強。例如: 濾波器:卷積用于應(yīng)用低通、高通、帶通等濾波器,去除不需要...

圖卷積網(wǎng)絡(luò)(Graph Convolutional Network,GCN)是一種用于處理圖結(jié)構(gòu)數(shù)據(jù)的深度學(xué)習(xí)模型。它在圖形數(shù)據(jù)上執(zhí)行卷積操作,類似于傳統(tǒng)的卷積神經(jīng)網(wǎng)絡(luò)(CNN)在圖像數(shù)據(jù)上執(zhí)行的操作,但是適用于不規(guī)則的圖結(jié)構(gòu)數(shù)據(jù)。...

分類:其它 時間:2024-05-16 閱讀:557 關(guān)鍵詞:圖卷積網(wǎng)絡(luò)

卷積是一種在數(shù)學(xué)和信號處理中廣泛應(yīng)用的運算方法,它通常被用于描述兩個函數(shù)之間的關(guān)系。在信號處理中,卷積可以將兩個信號進(jìn)行組合,以得到一個新的信號,該信號反映了這兩個原始信號之間的關(guān)系。 具體來說,假...

時間:2024-01-26 閱讀:2876 關(guān)鍵詞:卷積

深入洞察DSP:卷積在各領(lǐng)域的10個應(yīng)用

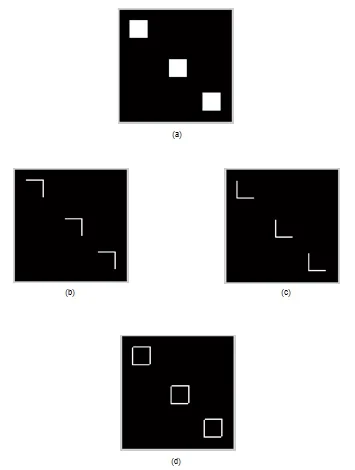

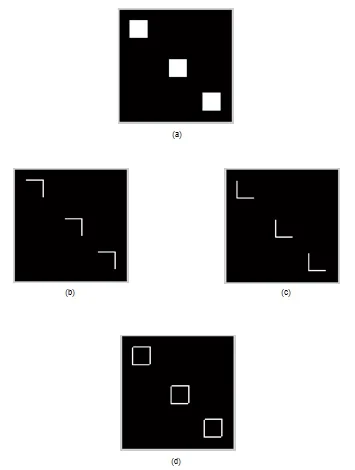

1. 圖像處理 空間域中的圖像處理是一個涉及像素操作技術(shù)的視覺豐富的研究領(lǐng)域。對圖像執(zhí)行不同的操作,將圖像簡單地視為二維數(shù)組。 通常,所有這些基于矩陣的運算都...

分類:單片機與DSP 時間:2023-07-18 閱讀:2448 關(guān)鍵詞:三腳可調(diào)調(diào)節(jié)器

深入了解DSP:10個卷積在各個領(lǐng)域的應(yīng)用

1.圖像處理空間域中的圖像處理是處理像素操作技術(shù)的視覺豐富的研究領(lǐng)域。對圖像執(zhí)行不同的操作,這些圖像被簡單地視為二維數(shù)組。通常,所有這些基于矩陣的操作都在較大矩陣...

Achronix - 實測!AlexNet卷積核在FPGA占90%資源仍跑750MHz|算力達(dá)288萬張圖像/秒

MLP_Conv2D是功能齊全的設(shè)計,可將2D輸入圖像與多個內(nèi)核同時進(jìn)行卷積。 該設(shè)計充分利用了MLP和BRAM模塊,每個MLP一個周期執(zhí)行12個int8乘法。此外,MLP列和BRAM塊均等級聯(lián)以...

分類:其它 時間:2020-06-15 閱讀:778 關(guān)鍵詞:Achronix - 實測!AlexNet卷積核在FPGA占90%資源仍跑750MHz算力達(dá)288萬張圖像/秒FPGA

使用TensorFlow框架演示了卷積神經(jīng)網(wǎng)絡(luò)在MNIST數(shù)據(jù)集上的應(yīng)用

Google產(chǎn)品分析Zlatan Kremonic介紹了卷積神經(jīng)網(wǎng)絡(luò)的機制,并使用TensorFlow框架演示了卷積神經(jīng)網(wǎng)絡(luò)在MNIST數(shù)據(jù)集上的應(yīng)用。 卷積神經(jīng)網(wǎng)絡(luò)(CNN)是一種前饋人工神經(jīng)網(wǎng)...

分類:其它 時間:2018-08-27 閱讀:1615 關(guān)鍵詞:使用TensorFlow框架演示了卷積神經(jīng)網(wǎng)絡(luò)在MNIST數(shù)據(jù)集上的應(yīng)用神經(jīng)網(wǎng)絡(luò),MNIST數(shù)據(jù)

摘要:本文對比了在加性高斯白噪聲(AWGN)信道下經(jīng)BPSK調(diào)制后的數(shù)據(jù)不編碼與添加卷積編碼后接收到的信道輸出的誤碼性能,并通過對比對卷積碼性能進(jìn)行分析。采用MATLAB自編...

分類:基礎(chǔ)電子 時間:2014-02-27 閱讀:8278 關(guān)鍵詞:卷積碼編碼和維特比譯碼性能的對比分析MATLAB卷積碼維特比譯碼

卷積編碼及Viterbi 解碼的FPGA 實現(xiàn)及應(yīng)用

摘要:卷積碼在現(xiàn)代無線通信系統(tǒng)中應(yīng)用十分廣泛,Viterbi譯碼是最常用的一種對卷積碼的譯碼算法。介紹了卷積編碼及Viterbi串行解碼的原理及其FPGA的實現(xiàn)。在保證系統(tǒng)性能的...

分類:通信與網(wǎng)絡(luò) 時間:2014-01-15 閱讀:2126 關(guān)鍵詞:卷積編碼及Viterbi 解碼的FPGA 實現(xiàn)及應(yīng)用卷積編碼Viterbi串行解碼FPGA

L-DACS1 中多速率卷積編碼器的設(shè)計與FPGA 實現(xiàn)

摘要:在L波段數(shù)字航空通信系統(tǒng)(L-DACS1 )中,不同類型的數(shù)據(jù)采用不同速率傳輸,為了降低信道的噪聲和畸變與多普勒頻移的影響,采用具有良好差錯控制能力的多速率卷積編...

分類:通信與網(wǎng)絡(luò) 時間:2013-06-19 閱讀:3171 關(guān)鍵詞:L-DACS1 中多速率卷積編碼器的設(shè)計與FPGA 實現(xiàn)L-DACS1多速率卷積編碼器

對于一般的線性分組碼(如循環(huán)碼、BCH碼等),它們的共同特點是:一個碼字的監(jiān)督單元僅與本碼組的k位信息碼元有關(guān),與其它碼字的碼元無關(guān)。而卷積碼的特點在于本組的碼元不僅與當(dāng)有輸入的k個信息有關(guān),而且還與前面m...

時間:2011-08-26 閱讀:1722

卷積碼是深度空間通信系統(tǒng)和無線通信系統(tǒng)中常用的一種差錯控制編碼。它克服了分組碼由于以碼塊為單位編譯碼而使分組間的相關(guān)信息丟失的缺點。(2,1,8)卷積碼在2G、3G通...

分類:通信與網(wǎng)絡(luò) 時間:2011-08-04 閱讀:3270 關(guān)鍵詞:基于FPGA的卷積碼譯碼器的方案卷積碼

基于FPGA的卷積編譯碼器的設(shè)計與實現(xiàn)

摘要:為了解決傳統(tǒng)的維特比譯碼器結(jié)構(gòu)復(fù)雜、譯碼速度慢、消耗資源大的問題,提出一種新型的適用于FPGA特點,路徑存儲與譯碼輸出并行工作,同步存儲路徑矢量和狀態(tài)矢量的譯...

分類:EDA/PLD/PLC 時間:2010-11-22 閱讀:4034 關(guān)鍵詞:基于FPGA的卷積編譯碼器的設(shè)計與實現(xiàn)卷積編譯碼器

摘要:介紹了咬尾卷積碼的和次譯碼算法的實現(xiàn)細(xì)節(jié)。給出了采用新的蝶形圖計算方法和環(huán)形內(nèi)存來節(jié)省硬件資源的實現(xiàn)方法,給出了次算法在FPGA上的實現(xiàn)結(jié)果。 0 引言 自...

分類:EDA/PLD/PLC 時間:2010-09-29 閱讀:5342 關(guān)鍵詞:一種高效咬尾卷積碼譯碼器的設(shè)計與仿真譯碼器咬尾卷積碼

“卷積和相關(guān)”在輸入信號上進(jìn)行卷積、反卷積、相關(guān)操作,其圖標(biāo)和接線端如圖1所示。 在程序框圖中添加“卷積和相關(guān)”時,或右鍵單擊圖標(biāo)并在快捷菜單中選擇“屬性”項...

分類:其它 時間:2008-09-20 閱讀:4796 關(guān)鍵詞:LabVIEW 8.2的卷積和相關(guān)信號運算

基于TMS320C54X的RS+變織+卷積的級聯(lián)糾錯碼

摘要:糾錯編碼被廣泛應(yīng)用在各種數(shù)字通訊、數(shù)字廣播和數(shù)據(jù)存儲系統(tǒng)中。隨著單片機、DSP和FPGA等器件的發(fā)展,越來越容易在各種通用硬件平臺上實現(xiàn)糾錯編碼。本文基于TI的54系列DSP,實現(xiàn)由常用RS碼、卷積編碼、Viterb...

分類:單片機與DSP 時間:2007-04-29 閱讀:1550 關(guān)鍵詞:基于TMS320C54X的RS+變織+卷積的級聯(lián)糾錯碼

摘 要:卷積碼是一種性能優(yōu)良的差錯控制編碼。本文在闡述卷積 碼編解碼器基本工作原理的基礎(chǔ)上,提出了在MAX+PlusⅡ開發(fā)平臺上基于VHDL語言設(shè)計 (2,1,6)卷 積碼編解碼器的方法。仿真實驗結(jié)果表明了該編解碼器的...

分類:通信與網(wǎng)絡(luò) 時間:2007-04-10 閱讀:2438 關(guān)鍵詞:基于VHDL語言的卷積碼編解碼器的設(shè)計

卷積碼+QPSK的中頻調(diào)制解調(diào)系統(tǒng)的FPGA實現(xiàn)

摘要:提出了一個采用(2,1,7)卷積碼+QPSK的中頻調(diào)制解調(diào)方案,并在Xilinx公司的100萬門FPGA芯片上實現(xiàn)了該系統(tǒng)。該系統(tǒng)在信噪比SNR為6dB左右時可實現(xiàn)速率超過1Mbit/s、誤碼率小于10-5的數(shù)據(jù)傳輸。關(guān)鍵詞:卷...

分類:EDA/PLD/PLC 時間:2007-04-03 閱讀:2564 關(guān)鍵詞:卷積碼+QPSK的中頻調(diào)制解調(diào)系統(tǒng)的FPGA實現(xiàn)1967FPGAMEMORYxc2v1000XILINX