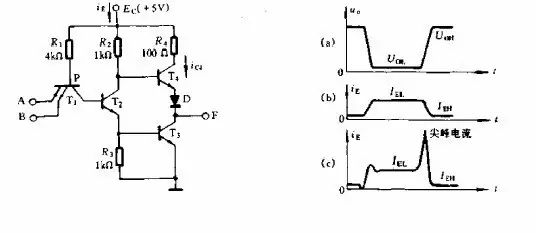

尖峰電流的形成在數(shù)字電路中,數(shù)字電路輸出高電平時(shí)從電源拉出的電流 Ioh 和低電平輸出時(shí)灌入的電流 Iol 大小通常不同,一般 Iol>Ioh。以 TTL 與非門為例,輸出電壓如右圖...

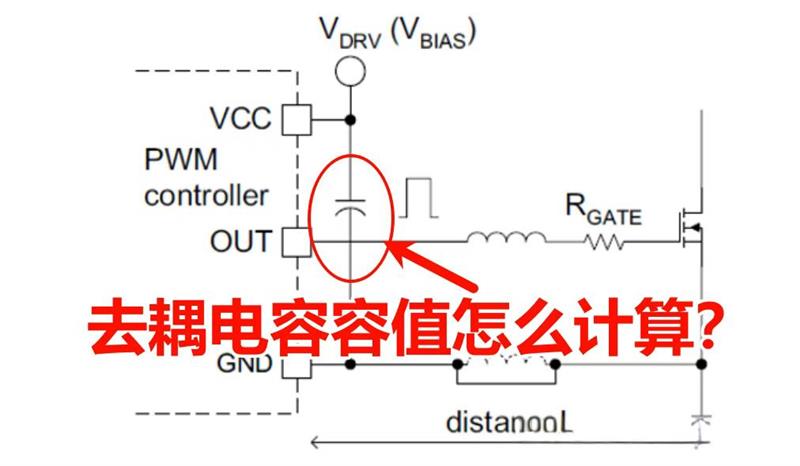

深度解析:柵極驅(qū)動(dòng)電路 VCC 電源去耦電容容值計(jì)算方法

在電子電路設(shè)計(jì)領(lǐng)域,MOSFET 柵極驅(qū)動(dòng)器電路的設(shè)計(jì)至關(guān)重要。而在該電路中,為 VCC 電源添加去耦電容這一操作,并非隨意為之。去耦電容容值的計(jì)算需要綜合考慮電路需求和實(shí)...

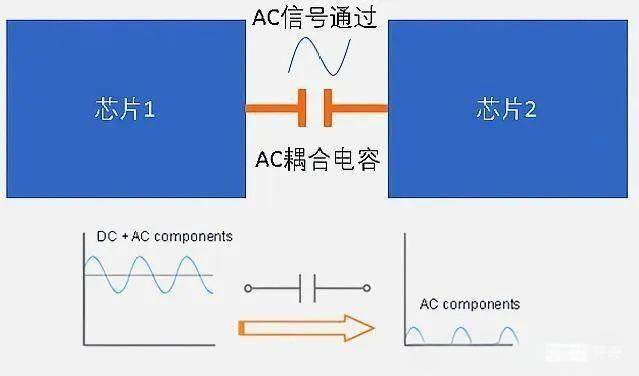

在硬件設(shè)計(jì)領(lǐng)域,搞硬件的人員通常會(huì)注意到芯片電源引腳旁一般會(huì)放置一個(gè)電容,且這個(gè)電容大多為 100nF,該電容也被稱為去耦電容(Decoupling Capacitor)。這一設(shè)計(jì)在硬件電路設(shè)計(jì)中極為常見,但為何常選 100nF 呢...

分類:電源技術(shù) 時(shí)間:2023-11-23 閱讀:0

時(shí)鐘數(shù)字IC通常需要大的瞬態(tài)電源電流。例如,大型微處理器可以在很短的時(shí)間內(nèi)消耗高達(dá) 10 A 的電流。隨著 IC 輸出的上升/下降時(shí)間縮短,我們需要以更高的速率提供瞬態(tài)能量...

分類:PCB技術(shù) 時(shí)間:2023-11-01 閱讀:2081 關(guān)鍵詞:去耦電容器

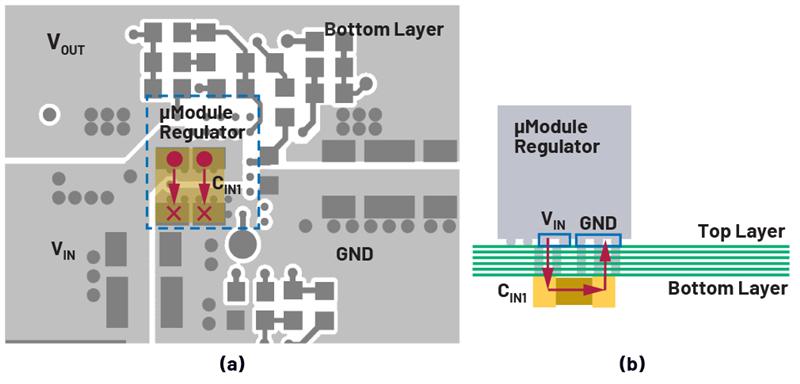

熱環(huán)路 PCB ESR 和 ESL 與去耦電容器位置的關(guān)系

LTM4638 是一款集成的 20 V IN、15 A 降壓轉(zhuǎn)換器模塊,采用微型 6.25 mm × 6.25 mm × 5.02 mm BGA 封裝。它具有高功率密度、快速瞬態(tài)響應(yīng)和高效率。該模塊內(nèi)部集成了一個(gè)...

分類:PCB技術(shù) 時(shí)間:2023-07-10 閱讀:1261 關(guān)鍵詞: PCB

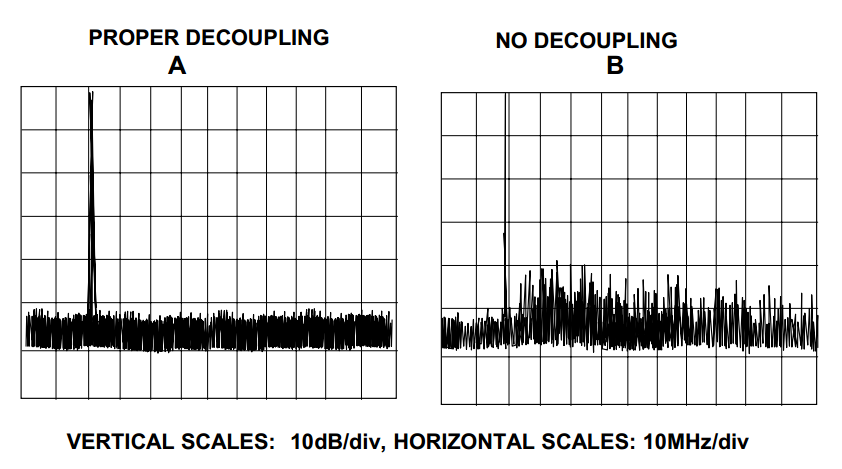

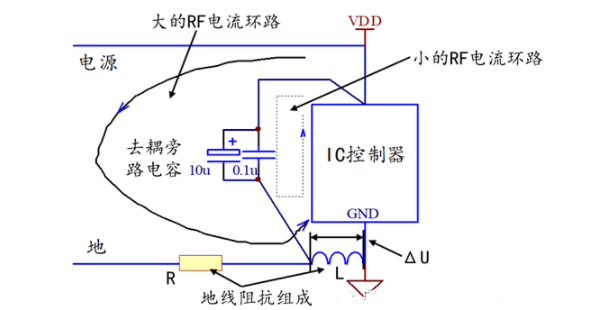

不良的電容器去耦會(huì)增加失真PCB 的電源和接地導(dǎo)體確實(shí)存在一些電感。如果我們?cè)噲D直接通過電源和接地導(dǎo)體提供設(shè)備的高頻電流,這種電感可能會(huì)導(dǎo)致問題。回想一下,電感兩端...

1、輸入電阻和輸出電阻 輸入電阻是用來衡量放大器對(duì)信號(hào)源的影響的一個(gè)性能指標(biāo)。輸入電阻越大,表明放大器從信號(hào)源取的電流越小,放大器輸入端得到的信號(hào)電壓也越大,即信號(hào)源電壓衰減的少。理論基礎(chǔ):Us=(Rs+Ri...

分類:元器件應(yīng)用 時(shí)間:2022-12-09 閱讀:534 關(guān)鍵詞:電阻

去耦濾波電容怎么布局?jǐn)[放,到底是先大后小還是先小后大?

對(duì)于噪聲敏感的IC電路,為了達(dá)到更好的濾波效果,通常會(huì)選擇使用多個(gè)不同容值的電容并聯(lián)方式,以實(shí)現(xiàn)更寬的濾波頻率,如在IC電源輸入端用1μF、100nF和10nF并聯(lián)可以實(shí)現(xiàn)更...

分類:元器件應(yīng)用 時(shí)間:2022-08-22 閱讀:1551 關(guān)鍵詞:電子

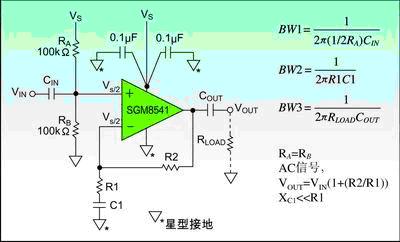

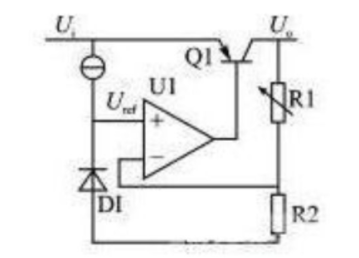

目前在許多手持設(shè)備、汽車以及計(jì)算機(jī)等設(shè)備只用單電源供電,但是單電源容易出現(xiàn)不穩(wěn)定問題,因此需要在電路外圍增加輔助器件以提高穩(wěn)定性。在電路圖1中展示了單電源供電運(yùn)...

電路的設(shè)計(jì)中存在很多 電磁干擾(EMI) 問題, 去耦電容 的應(yīng)用場(chǎng)景就是減小電磁干擾,這一過程衍生出了另一個(gè)概念—— 電磁兼容(EMC) 。 電磁干擾(EMI)的例子? 1、靜電放電(ESD) 冬天的時(shí)候,尤其是空氣比較...

分類:元器件應(yīng)用 時(shí)間:2022-04-01 閱讀:943 關(guān)鍵詞:去耦電容

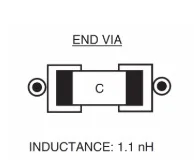

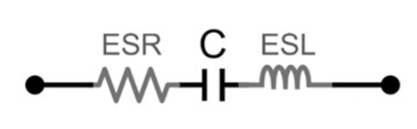

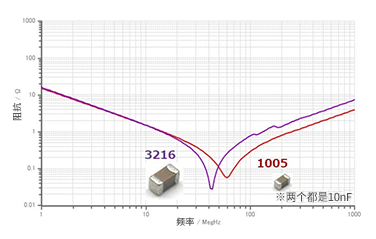

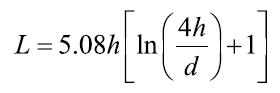

去耦電容的有效使用方法的第二個(gè)要點(diǎn)是降低電容的ESL(即等效串聯(lián)電感)。雖說是“降低ESL”,但由于無法改變單個(gè)產(chǎn)品的ESL本身,因此這里是指“即使容值相同,也要使用ESL...

分類:元器件應(yīng)用 時(shí)間:2021-09-17 閱讀:980 關(guān)鍵詞:如何降低去耦電容的ESL(等效串聯(lián)電感)去耦電容

從電源系統(tǒng)的角度進(jìn)行去耦設(shè)計(jì)

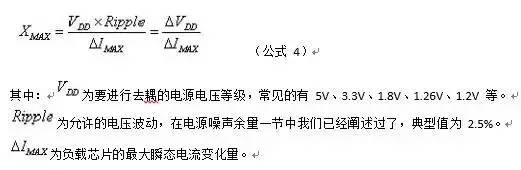

四、從電源系統(tǒng)的角度進(jìn)行去耦設(shè)計(jì) 這一節(jié)就來講講另一種方法,從電源系統(tǒng)的角度進(jìn)行去耦設(shè)計(jì)。該方法本著這樣一個(gè)原則:在感興趣的頻率范圍內(nèi),使整個(gè)電源分配系統(tǒng)阻抗...

分類:電源技術(shù) 時(shí)間:2021-08-06 閱讀:496 關(guān)鍵詞:從電源系統(tǒng)的角度進(jìn)行去耦設(shè)計(jì)電源系統(tǒng)

去耦電容有效使用方法的要點(diǎn)大致可以分為以下兩種。另外,還有其他幾點(diǎn)需要注意。 要點(diǎn)1:使用多個(gè)去耦電容 要點(diǎn)2:降低電容的ESL(等效串聯(lián)電感) 其他注意事項(xiàng) 要點(diǎn)1:使用多個(gè)去耦電容 去耦電容的...

分類:元器件應(yīng)用 時(shí)間:2021-08-04 閱讀:426 關(guān)鍵詞:去耦電容的有效使用方法去耦電容

EMC基礎(chǔ):去耦電容的有效使用方法-要點(diǎn)2

上一篇文章介紹了“去耦電容的有效使用方法”的要點(diǎn)1“使用多個(gè)去耦電容”。本文將介紹“要點(diǎn)2”。 要點(diǎn)2:降低電容的ESL 去耦電容的有效使用方法的第二個(gè)要點(diǎn)是降低...

分類:元器件應(yīng)用 時(shí)間:2021-03-24 閱讀:720 關(guān)鍵詞:EMC基礎(chǔ):去耦電容的有效使用方法-要點(diǎn)2去耦電容

旁路和去耦是指防止有用能量從一個(gè)電路傳到另一個(gè)電路中,并改變?cè)肼暷芰康膫鬏斅窂剑瑥亩岣唠娫捶峙渚W(wǎng)絡(luò)的品質(zhì)。它有三個(gè)基本概念:電源、地平面,元件和內(nèi)層的電源連接...

分類:PCB技術(shù) 時(shí)間:2021-01-08 閱讀:970 關(guān)鍵詞:淺談PCB中的去耦電容設(shè)計(jì)PCB

對(duì)于已經(jīng)知道了電容的具體特性和適用范圍,以及去耦原理,那么就知道了去耦的具體方法了嗎?不是的,下面我們將講解一下,具體安裝到電路板上之后的去耦原理以及具體如何防...

分類:元器件應(yīng)用 時(shí)間:2021-01-04 閱讀:610 關(guān)鍵詞:去耦原理以及具體如何防止電容的準(zhǔn)則電容

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號(hào)完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號(hào)鏈中的濾波與功耗管理