在當今科技飛速發(fā)展的時代,系統(tǒng)的可靠性和穩(wěn)定性至關(guān)重要。容錯控制技術(shù)的研究雖面臨著諸多挑戰(zhàn),但近年來,魯棒控制理論、模糊控制、神經(jīng)網(wǎng)絡(luò)控制等相關(guān)領(lǐng)域的深入發(fā)展,為其帶來了新的機遇和條件。同時,計算機控...

基于MPC860芯片和MlPC860P芯片實現(xiàn)硬件容錯專用計算機的設(shè)計

測控設(shè)備在信號檢測、工業(yè)控制、醫(yī)療儀器、航空航天等領(lǐng)域應(yīng)用十分廣泛。目前測控系統(tǒng)大多是以工業(yè)控制計算機作為控制中心。但是這種方法主要有以下缺點:一是工業(yè)控制計算...

時間:2021-01-28 閱讀:501 關(guān)鍵詞:基于MPC860芯片和MlPC860P芯片實現(xiàn)硬件容錯專用計算機的設(shè)計MlPC860P芯片

我們常接觸到晶體三級管,對它的使用也比較熟悉,相對來說對晶體場效應(yīng)管就陌生一點,但是,由于場效應(yīng)管有其獨特的優(yōu)點,例輸入阻抗高,噪聲低,熱穩(wěn)定性好等,在我們的使用中也是屢見不鮮。我們知道場效應(yīng)晶體管的...

分類:元器件應(yīng)用 時間:2019-01-03 閱讀:664 關(guān)鍵詞:不容錯過!場效應(yīng)晶體管使用詳解場效應(yīng)晶體管

家族中有三大成員,分別是高速CAN、、單線CAN。其中又叫低速CAN,它與最常用的高速CAN有什么異同呢?這里將與大家分享下對的認識。 一、容錯CAN的起源 1986年Bosch在S...

時間:2017-10-27 閱讀:1046 關(guān)鍵詞:容錯CAN,CAN-bus

摘要:仿照自然界的碳基生物進化過程,在FPGA內(nèi)部實現(xiàn)了可控的硅基進化。針對電子系統(tǒng)常見的SA故障,提出了基于演化硬件技術(shù)的內(nèi)進化容錯模型,通過在FPGA內(nèi)部裝載Microbla...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時間:2013-12-31 閱讀:1789 關(guān)鍵詞:內(nèi)進化容錯模型設(shè)計及其可靠性分析FPGA容錯模型進化硬件

大型數(shù)據(jù)存儲中心高智能容錯雙總線系統(tǒng)設(shè)計方案

1 概述 大型數(shù)據(jù)中心存儲中心機房專門為數(shù)據(jù)進行存儲保存,確保數(shù)據(jù)萬無一失,地理位置相對偏僻安全,不容易發(fā)現(xiàn),預(yù)計機柜500架,每個機架規(guī)劃容量按4kVA計算,實際使用容量2.5kW.為保證數(shù)據(jù)存儲中心機房內(nèi)所有...

分類:電源技術(shù) 時間:2012-10-17 閱讀:2787 關(guān)鍵詞:大型數(shù)據(jù)存儲中心高智能容錯雙總線系統(tǒng)設(shè)計方案數(shù)據(jù)存儲中心高智能容錯雙總線系統(tǒng)

簡述網(wǎng)絡(luò)存儲系統(tǒng)容錯編碼技術(shù)進展

1 存儲容錯編碼評價指標 近20年來,隨著計算機技術(shù)的迅猛發(fā)展,大規(guī)模存儲系統(tǒng)的發(fā)展也十分迅速。當前,普通PC機的存儲器的容量已經(jīng)達到了太比特級別,這較之20年前的20...

分類:模擬技術(shù) 時間:2011-08-26 閱讀:2403 關(guān)鍵詞:存儲存儲系統(tǒng)

引言 在數(shù)字電路設(shè)計中,集成度、質(zhì)量和可靠性起著十分重要的作用,數(shù)字電路出現(xiàn)故障的幾率隨著其規(guī)模和復(fù)雜度的增加而增大。因此,自診斷和自修復(fù)對數(shù)字電路容錯技術(shù)發(fā)...

摘要: 隨著計算機技術(shù)的發(fā)展,計算機系統(tǒng)的可靠性越來越受到人們的重視,而容錯技術(shù)是提高可靠性的一種有效方法。本文研究了計算機容錯技術(shù)的各種方法,如硬件容錯、信息容...

分類:其它 時間:2010-11-17 閱讀:3340 關(guān)鍵詞:計算機系統(tǒng)的容錯技術(shù)方法

0 前言 自HALME A等于1996年首次研制出球形機器人以來,控制系統(tǒng)一直被視為球形機器人研究領(lǐng)域的關(guān)鍵問題。球形機器人結(jié)構(gòu)的特殊性和控制方法的復(fù)雜性使目前的研究內(nèi)容...

分類:工業(yè)電子 時間:2010-09-06 閱讀:3468 關(guān)鍵詞:基于容錯策略的球形機器人控制系統(tǒng)

容錯實時系統(tǒng)的研究主要集中在兩個方面:① 改進實時調(diào)度算法,使之確保實時任務(wù)在正常運行和遇到錯誤時,均能在規(guī)定時限到來以前獲得正確的輸出。② 將過去應(yīng)用于普通計算機系統(tǒng)中的冗余容錯策略移植到實時系統(tǒng)中。...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時間:2010-08-31 閱讀:1693 關(guān)鍵詞:嵌入式雙機容錯實時系統(tǒng)的設(shè)計雙機容

SRAMFPGAMuxTree結(jié)構(gòu)模型的可容錯全加器設(shè)計

摘要:在SRAMFPGA的MuxTree結(jié)構(gòu)模型的基礎(chǔ)上,進行了一個具有容錯功能的一位全加器的設(shè)計和實現(xiàn)。文中介紹了MuxTree結(jié)構(gòu)模型的原理,并給出了基于該結(jié)構(gòu)模型容錯全加器的設(shè)計過程及系統(tǒng)邏輯構(gòu)成。同時,對該容錯系統(tǒng)...

分類:其它 時間:2007-05-25 閱讀:2112 關(guān)鍵詞:SRAMFPGAMuxTree結(jié)構(gòu)模型的可容錯全加器設(shè)計2003XILINXTP302

容錯系統(tǒng)中的自校驗技術(shù)及實現(xiàn)方法

摘要:闡述了自校驗技術(shù)在容錯系統(tǒng)中的作用,給出了自校驗網(wǎng)絡(luò)實現(xiàn)原理及實現(xiàn)方法,指出用VHDL語言結(jié)合FPGA/CPLD是實現(xiàn)大規(guī)模自校驗網(wǎng)絡(luò)的有效途徑。關(guān)鍵詞:容錯自校驗完全自校驗VHDLFPGA/CPLD容錯是容忍錯誤的簡稱...

分類:EDA/PLD/PLC 時間:2007-04-29 閱讀:1388 關(guān)鍵詞:容錯系統(tǒng)中的自校驗技術(shù)及實現(xiàn)方法

容錯技術(shù)在分布式多層應(yīng)用系統(tǒng)中的實現(xiàn)

【論文摘要】在分布式多層應(yīng)用系統(tǒng)中,把應(yīng)用程序服務(wù)器分布在兩臺或更多的計算機中執(zhí)行,根據(jù)負載平衡的原理,客戶端應(yīng)用程序連接到其中一臺計算機的應(yīng)用程序服務(wù)器要求服務(wù)。如果客戶端應(yīng)用程序當前連接的應(yīng)用程序...

分類:其它 時間:2007-04-29 閱讀:2239 關(guān)鍵詞:容錯技術(shù)在分布式多層應(yīng)用系統(tǒng)中的實現(xiàn)200220012000

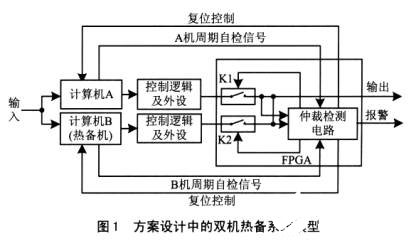

摘要:為滿足對安全關(guān)鍵領(lǐng)域日益增長的可靠性需求,提出一種基于松耦合多處理器體系結(jié)構(gòu)的雙機容錯實時嵌入式系統(tǒng)設(shè)計方案。該方案無縫整合了計算機硬件級、操作系統(tǒng)級、應(yīng)用級的容錯技術(shù),以達到從整體上提高系統(tǒng)可...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時間:2007-04-28 閱讀:1327 關(guān)鍵詞:雙機容錯實時嵌入式系統(tǒng)設(shè)計與分析

隨著各種電路和芯片的性能(速度、集成度等)不斷提高,尤其是在軍事、航空航天等用途中對可靠性的要求往往是位的,人們對于系統(tǒng)的可靠性方面的要求日益增加,這對電路系統(tǒng)的設(shè)計和制造都提出了嚴格的目標要求。 存儲...

分類:其它 時間:2007-04-17 閱讀:1530 關(guān)鍵詞:基于CPLD的容錯存儲器的 設(shè)計實現(xiàn)EPM7128

基于雙DSP的磁軸承數(shù)字控制器容錯設(shè)計[日期:2006-3-13]來源:電子設(shè)計應(yīng)用作者:余同正徐龍祥[字體:大中小]摘要:本文介紹了應(yīng)用于磁軸承的雙DSP熱備容錯控制方案,該方案采用時鐘同步技術(shù),由總線表決模塊實現(xiàn)系...

分類:單片機與DSP 時間:2007-04-03 閱讀:1871 關(guān)鍵詞:基于雙DSP的磁軸承數(shù)字控制器容錯設(shè)計74LS123IDT7133RS-232