什么是DDR3L內(nèi)存?DDR3L和DDR3內(nèi)存哪個(gè)好?DDR3L和DDR3內(nèi)存的區(qū)別

什么是DDR3L內(nèi)存? DDR3L內(nèi)存是一種低電壓雙倍數(shù)據(jù)率第三代同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(DDR3 SDRAM),它是DDR3內(nèi)存的低電壓版本。DDR3L內(nèi)存通常工作在1.35V電壓,相比標(biāo)準(zhǔn)的DDR3內(nèi)存(工作電壓為1.5V),能夠降低...

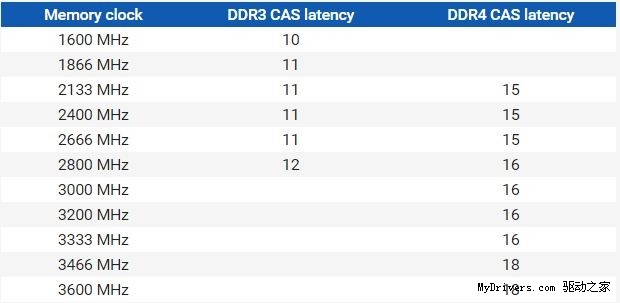

DDR3和DDR4是計(jì)算機(jī)內(nèi)存模塊的兩種標(biāo)準(zhǔn),它們?cè)跀?shù)據(jù)傳輸速度、能效、密度等方面有所不同。以下是它們的主要特點(diǎn): DDR3(Double Data Rate 3) 數(shù)據(jù)傳輸速度: DDR3內(nèi)存的數(shù)據(jù)傳輸速度相對(duì)較慢,最高可達(dá)每秒16...

時(shí)間:2024-03-07 閱讀:610 關(guān)鍵詞:DDR3,DDR4

在內(nèi)存的關(guān)鍵指標(biāo)中,容量、速度和時(shí)序是常被提及的參數(shù),速度普遍意義上被認(rèn)為是內(nèi)存帶寬。 Intel第六代酷睿Skylake處理器發(fā)布后,帶來(lái)了對(duì)DDR4的全面支持。雖然DDR4內(nèi)...

PCB的SI設(shè)計(jì):DDR2、DDR3應(yīng)該是這樣的

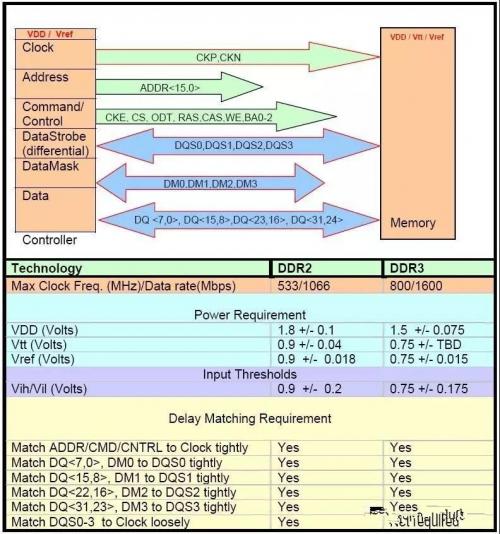

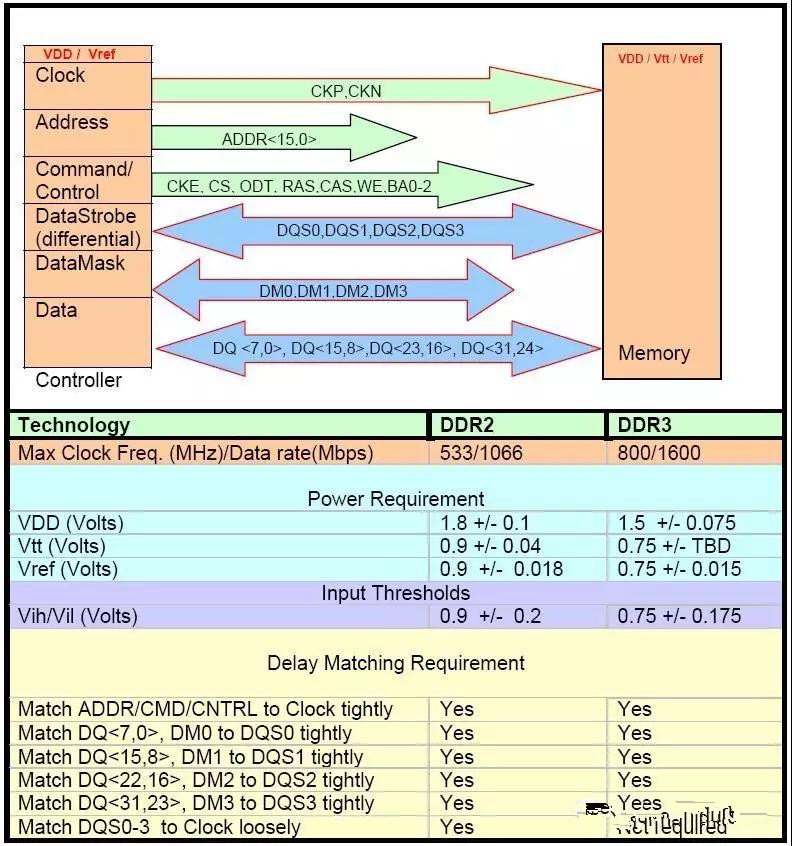

本文章主要涉及到對(duì)DDR2和DDR3在設(shè)計(jì)印制線路板(PCB)時(shí),考慮信號(hào)完整性和電源完整性的設(shè)計(jì)事項(xiàng),這些是具有相當(dāng)大的挑戰(zhàn)性的。文章重點(diǎn)是討論在盡可能少的PCB層數(shù),特別...

分類:PCB技術(shù) 時(shí)間:2019-09-02 閱讀:1927 關(guān)鍵詞:PCB

DDR2和DDR3的PCB信號(hào)完整性設(shè)計(jì)

作為電子與通信工程及其相關(guān)的資料。對(duì)于那些從事軟硬件開(kāi)發(fā)、集成電路設(shè)計(jì)、系統(tǒng)設(shè)計(jì)的工程技術(shù)人員來(lái)說(shuō)也是一本很好的文章。 它主要涉及到對(duì)DDR2和DDR3在設(shè)計(jì)印制線路...

分類:通信與網(wǎng)絡(luò) 時(shí)間:2019-07-30 閱讀:1306 關(guān)鍵詞:PCB信號(hào)

針對(duì)DDR2-800和DDR3的PCB信號(hào)完整性設(shè)計(jì)

本文章主要涉及到對(duì)DDR2和DDR3在設(shè)計(jì)印制線路板(PCB)時(shí),考慮信號(hào)完整性和電源完整性的設(shè)計(jì)事項(xiàng),這些是具有相當(dāng)大的挑戰(zhàn)性的。文章重點(diǎn)是討論在盡可能少的PCB層數(shù),特別...

分類:通信與網(wǎng)絡(luò) 時(shí)間:2019-07-24 閱讀:1647 關(guān)鍵詞:DDR2-800,DDR3,PCB信號(hào)

基于FPGA的DDR3 SDRAM控制器用戶接口設(shè)計(jì)

摘要:為了滿足高速圖像數(shù)據(jù)采集系統(tǒng)中對(duì)高帶寬和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的設(shè)計(jì)方法,提出了一種基于Verilog-HDL 語(yǔ)言的DDR3 SDRAM 控制器用...

時(shí)間:2017-11-17 閱讀:1217 關(guān)鍵詞:ddr3,控制器

基于FPGA的DDR3多端口讀寫存儲(chǔ)管理系統(tǒng)設(shè)計(jì)

機(jī)載視頻圖形顯示系統(tǒng)主要實(shí)現(xiàn)2D圖形的繪制,構(gòu)成各種飛行參數(shù)畫面,同時(shí)疊加實(shí)時(shí)的外景視頻。由于FPGA具有強(qiáng)大邏輯資源、豐富IP核等優(yōu)點(diǎn),基于FPGA的嵌入式系統(tǒng)架構(gòu)是機(jī)載...

分類:EDA/PLD/PLC 時(shí)間:2015-03-12 閱讀:3981 關(guān)鍵詞:基于FPGA的DDR3多端口讀寫存儲(chǔ)管理系統(tǒng)設(shè)計(jì)FPGADDR3

S2C提供滿足使用大容量或高性能DDR3內(nèi)存的QuadE V7

導(dǎo)讀:近日,SoC/ASIC快速原型解決方案領(lǐng)先的供應(yīng)商S2C宣布提供滿足使用大容量或高性能DDR3內(nèi)存的QuadEV7.全新的QuadEV7能夠擴(kuò)充遠(yuǎn)程管理功能,幫助設(shè)計(jì)人員向著實(shí)現(xiàn)“云端”原型驗(yàn)證再邁進(jìn)一步。據(jù)了解,S2C的QuadE...

分類:EDA/PLD/PLC 時(shí)間:2014-02-28 閱讀:2611 關(guān)鍵詞:S2C提供滿足使用大容量或高性能DDR3內(nèi)存的QuadE V7S2CQuadE V7FPGA時(shí)鐘編程

DS34S132 32端口TDM - over –Packet IC采用外部DDR同步DRAM (DDR1)存儲(chǔ)器緩存數(shù)據(jù)。內(nèi)存空間需提供足夠的緩存區(qū)域,以支持256條偽線(PW)/綁定中每一偽線的256ms數(shù)據(jù)包延遲變化(PDV)。如果數(shù)據(jù)包交換網(wǎng)絡(luò)(PSN...

分類:其它 時(shí)間:2012-01-03 閱讀:4067 關(guān)鍵詞:配合DS34S132使用的DDR3存儲(chǔ)器模塊

爾必達(dá)申明40nm制程2Gb DDR3內(nèi)存芯片成功開(kāi)發(fā)

爾必達(dá)公司近日宣布已經(jīng)完成了40nm制程2Gb密度DDR3 SDRAM內(nèi)存芯片的研發(fā)工作,今年11月份這種芯片將進(jìn)入送樣階段,年底前則可實(shí)現(xiàn)正式批量供貨。據(jù)集成電路設(shè)計(jì)行業(yè)的消息來(lái)源稱,預(yù)見(jiàn)到SDRAM內(nèi)存將出現(xiàn)供應(yīng)短缺的局...

分類:嵌入式系統(tǒng)/ARM技術(shù) 時(shí)間:2011-09-02 閱讀:1764 關(guān)鍵詞:DDR3芯片

基于DDR3存儲(chǔ)器接口控制器IP核的視頻數(shù)據(jù)處理

引言 與過(guò)去幾代(DDR和DDR2)器件相比,DDR3存儲(chǔ)器器件有了明顯的進(jìn)步。DDR3存儲(chǔ)器系統(tǒng)可以大大提升各種數(shù)據(jù)處理應(yīng)用的性能。為了充分利用和發(fā)揮DDR3存儲(chǔ)器的優(yōu)點(diǎn),使用一個(gè)高效且易于使用的DDR3存儲(chǔ)器接口控制...

分類:其它 時(shí)間:2011-08-03 閱讀:4276 關(guān)鍵詞:基于DDR3存儲(chǔ)器接口控制器IP核的視頻數(shù)據(jù)處理

速度在不斷飆升!AMD的AM2接口K8架構(gòu)處理器引入最高DDR2800的支持,而Intel也在7月23日發(fā)布了萬(wàn)眾期待的Conroe處理器并進(jìn)行史上規(guī)模最大的"恐怖襲擊";電腦市場(chǎng)似乎在2006年已經(jīng)提前進(jìn)入了DDR2800的極速時(shí)代。RD600支

分類:其它 時(shí)間:2011-07-30 閱讀:3808 關(guān)鍵詞:內(nèi)存DDR2和DDR3有什么不同

完備的DDR2和DDR3存儲(chǔ)器電源管理方案MAX17000A

MAX17000A脈寬調(diào)制(PWM)控制器為筆記本電腦的DDR、DDR2、DDR3存儲(chǔ)器提供完整的電源方案。該器件集成了一路降壓控制器、一路可源出/吸入電流的LDO穩(wěn)壓器以及一路基準(zhǔn)緩沖器...

分類:電源技術(shù) 時(shí)間:2010-11-25 閱讀:4230 關(guān)鍵詞:完備的DDR2和DDR3存儲(chǔ)器電源管理方案MAX17000AMAX17000A

如何實(shí)現(xiàn)FPGA到DDR3 SDRAM存儲(chǔ)器的連接

采用90nm工藝制造的DDR3 SDRAM存儲(chǔ)器架構(gòu)支持總線速率為600 Mbps-1.6 Gbps (300-800 MHz)的高帶寬,工作電壓低至1.5V,因此功耗小,存儲(chǔ)密度更可高達(dá)2Gbits。該架構(gòu)無(wú)疑速度更快,容量更大,單位比特的功耗更低,但...

分類:其它 時(shí)間:2010-04-29 閱讀:6978 關(guān)鍵詞:如何實(shí)現(xiàn)FPGA到DDR3 SDRAM存儲(chǔ)器的連接FPGASDRAM存儲(chǔ)器DDR3

用中檔FPGA實(shí)現(xiàn)高速DDR3存儲(chǔ)器控制器

引言 由于系統(tǒng)帶寬不斷的增加,因此針對(duì)更高的速度和性能,設(shè)計(jì)人員對(duì)存儲(chǔ)技術(shù)進(jìn)行了優(yōu)化。下一代雙數(shù)據(jù)速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多...

分類:其它 時(shí)間:2010-01-22 閱讀:6887 關(guān)鍵詞:用中檔FPGA實(shí)現(xiàn)高速DDR3存儲(chǔ)器控制器DDR3存儲(chǔ)器控制器FPGA

HyperCloud的DDR3 RDIMM內(nèi)存模塊限度地允許384 GB內(nèi)存用在雙插槽服務(wù)器。該模塊采用的秩乘法ASIC技術(shù),從而完全替代帶有16Gb vRank RDIMM的三個(gè)存儲(chǔ)器通道。 四個(gè)物理組...

分類:其它 時(shí)間:2009-12-23 閱讀:3244 關(guān)鍵詞:Netlist推出提高服務(wù)器使用的DDR3模塊DDR3模塊

Inphi 推出提高DDR3系統(tǒng)容量和速度的隔離存儲(chǔ)緩沖器

iMB01-GS02隔離存儲(chǔ)緩沖器是單芯片,通過(guò)緩沖數(shù)據(jù)和尋址線降低存儲(chǔ)器控制器上負(fù)載。通過(guò)隔離CPU和存儲(chǔ)元器件,緩沖存儲(chǔ)器,I/O,控制和數(shù)據(jù)信號(hào),DDR3存儲(chǔ)器DIMM模塊(稱為L(zhǎng)...

分類:其它 時(shí)間:2009-12-17 閱讀:3872 關(guān)鍵詞:Inphi 推出提高DDR3系統(tǒng)容量和速度的隔離存儲(chǔ)緩沖器存儲(chǔ)緩沖器DDR3

基于Stratix III的DDR3 SDRAM控制器設(shè)計(jì)

摘要:本文介紹了DDR3 SDRAM 的基本特點(diǎn)和主要操作時(shí)序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設(shè)計(jì)方法。詳述了控制器基本結(jié)構(gòu)和設(shè)計(jì)思想,分析了各模塊功能與...

分類:其它 時(shí)間:2009-12-07 閱讀:5298 關(guān)鍵詞:基于Stratix III的DDR3 SDRAM控制器設(shè)計(jì)DDR3 SDRAM控制器

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號(hào)完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號(hào)鏈中的濾波與功耗管理