高速PCB信號完整性(SI)設(shè)計(jì)核心實(shí)操規(guī)范

隨著電子設(shè)備向高頻化、高傳輸速率升級,DDR5(4800Mbps)、PCIe4.0(16Gbps)、USB3.2(10Gbps)等高速接口已成為主流配置,信號完整性(SignalIntegrity,SI)已從“優(yōu)化項(xiàng)”成為“必選項(xiàng)”。低速PCB設(shè)計(jì)中“能連通...

分類:PCB技術(shù) 時(shí)間:2026-04-10 閱讀:344

在PCB設(shè)計(jì)過程中,電源平面的分割或者是地平面的分割,會(huì)導(dǎo)致平面的不完整,這樣信號走線的時(shí)候,它的參考平面就會(huì)出現(xiàn)從一個(gè)電源面跨接到另一個(gè)電源面,這種現(xiàn)象我們就叫做信號跨分割。 跨分割現(xiàn)象示意圖 跨...

分類:PCB技術(shù) 時(shí)間:2020-09-02 閱讀:632 關(guān)鍵詞:PCB信號跨分割線怎么處理?PCB信號

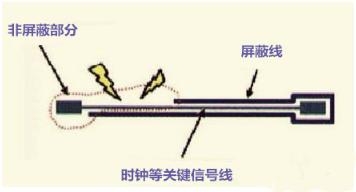

高速信號走線屏蔽規(guī)則 在高速的 PCB 設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會(huì)造成 EMI 的泄漏。建議屏蔽線,每 1000mil,打孔接地。 規(guī)則二 高速信號的走...

分類:PCB技術(shù) 時(shí)間:2020-08-17 閱讀:535 關(guān)鍵詞:高速PCB信號走線規(guī)則PCB信號

較多的PCB工程師,他們經(jīng)常畫電腦主板,對Allegro等優(yōu)秀的工具非常的熟練,但是,非常可惜的是,他們居然很少知道如何進(jìn)行阻抗控制,如何使用工具進(jìn)行信號完整性分析。如何使用IBIS模型我覺得真正的PCB高手應(yīng)該還是...

分類:PCB技術(shù) 時(shí)間:2019-09-30 閱讀:652 關(guān)鍵詞:PCB信號

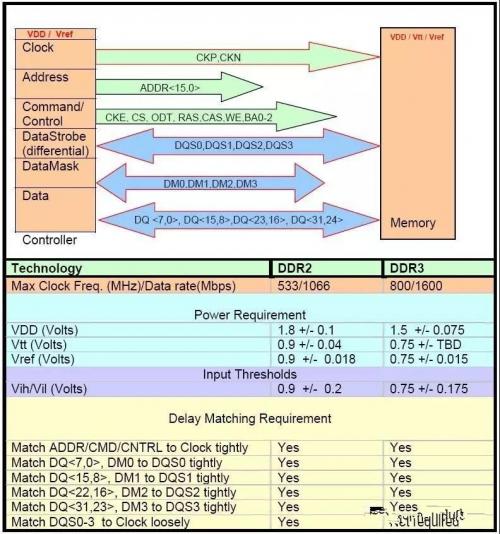

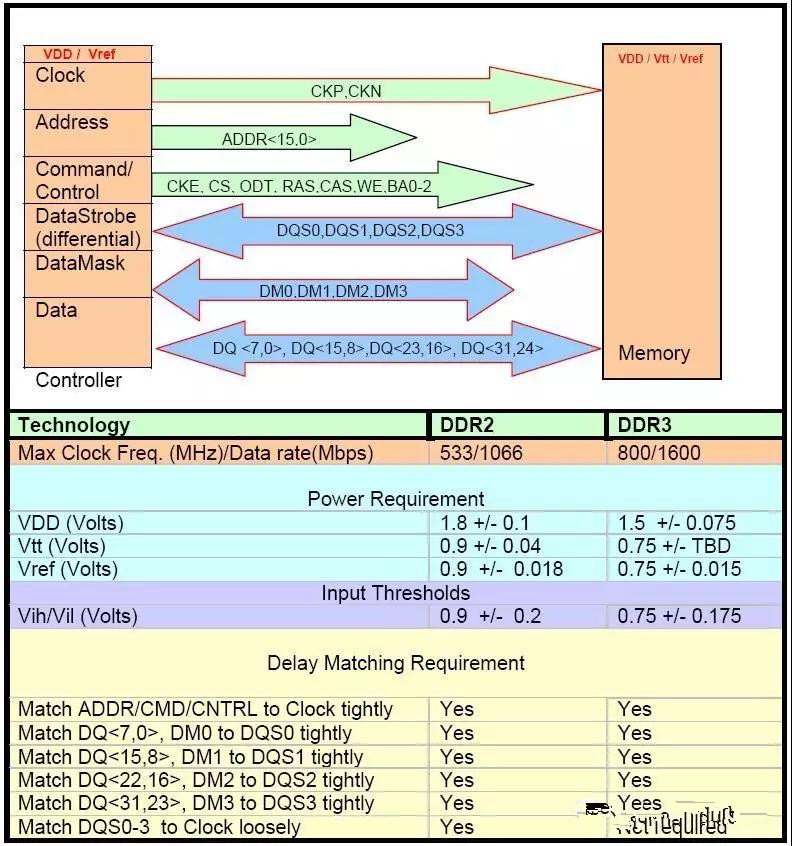

作為電子與通信工程及其相關(guān)的資料。對于那些從事軟硬件開發(fā)、集成電路設(shè)計(jì)、系統(tǒng)設(shè)計(jì)的工程技術(shù)人員來說也是一本很好的文章。 它主要涉及到對DDR2和DDR3在設(shè)計(jì)印制線路...

分類:通信與網(wǎng)絡(luò) 時(shí)間:2019-07-30 閱讀:1306 關(guān)鍵詞:PCB信號

針對DDR2-800和DDR3的PCB信號完整性設(shè)計(jì)

本文章主要涉及到對DDR2和DDR3在設(shè)計(jì)印制線路板(PCB)時(shí),考慮信號完整性和電源完整性的設(shè)計(jì)事項(xiàng),這些是具有相當(dāng)大的挑戰(zhàn)性的。文章重點(diǎn)是討論在盡可能少的PCB層數(shù),特別...

分類:通信與網(wǎng)絡(luò) 時(shí)間:2019-07-24 閱讀:1647 關(guān)鍵詞:DDR2-800,DDR3,PCB信號

規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。 圖1 高速信號線 規(guī)則二:...

分類:PCB技術(shù) 時(shí)間:2017-08-25 閱讀:1127 關(guān)鍵詞:9大硬件工程師談高速PCB信號走線規(guī)則

規(guī)則一:高速信號走線屏蔽規(guī)則 在高速的設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000m...

分類:PCB技術(shù) 時(shí)間:2017-08-17 閱讀:1984 關(guān)鍵詞:PCB,硬件工程師

信號完整性(SignalIntegrity,SI)是指信號在信號線上的質(zhì)量,即信號在電路中以正確的時(shí)序和電壓作出響應(yīng)的能力。如果電路中信號能夠以要求的時(shí)序、持續(xù)時(shí)間和電壓幅度到達(dá)接收器,則可確定該電路具有較好的信號完整...

分類:PCB技術(shù) 時(shí)間:2008-10-11 閱讀:2317 關(guān)鍵詞:PCB信號完整性PCB

PCB信號隔離技術(shù)是使數(shù)字或模擬信號在發(fā)送時(shí)不存在穿越發(fā)送和接收端之間屏障的電流連接。這允許發(fā)送和接收端外的地或基準(zhǔn)電平之差值可以高達(dá)幾千伏,并且防止可能損害信號的不同地電位之間的環(huán)路電流,主要應(yīng)用在...

分類:光電顯示/LED照明 時(shí)間:2008-09-02 閱讀:2262 關(guān)鍵詞:PCB信號隔離技術(shù)PCB

摘 要:從信號完整性分析設(shè)計(jì)規(guī)則、完整性分析仿真器、波形分析器等三個(gè)方面說明了如何利用Protel 99的信號完整性分析功能進(jìn)行印刷電路板的設(shè)計(jì)。 關(guān)鍵詞:信號完整性;電磁干擾;波形分析器 引言 ...

分類:PCB技術(shù) 時(shí)間:2007-11-16 閱讀:7732 關(guān)鍵詞:基于Protel 99的PCB信號完整性分析

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號鏈中的濾波與功耗管理