基于FPGA器件實(shí)現(xiàn)有限沖激響應(yīng)濾波器的方案設(shè)計(jì)

一個(gè)模擬集成運(yùn)算放大器可實(shí)現(xiàn)一個(gè)二階濾波器,高階濾波器可由二階濾波器串聯(lián)而成。然而,無源元器件實(shí)現(xiàn)濾波器的誤差值為1.5%或更高,這需要提高元器件的性能。濾波器的典型的調(diào)試方法是不斷的更換元器件值。而且...

分類:元器件應(yīng)用 時(shí)間:2020-11-24 閱讀:432 關(guān)鍵詞:基于FPGA器件實(shí)現(xiàn)有限沖激響應(yīng)濾波器的方案設(shè)計(jì)FPGA器件

基于Fusion系列FPGA器件實(shí)現(xiàn)水溫測控系統(tǒng)的設(shè)計(jì)

在遙測、遙控領(lǐng)域中,常常使用工業(yè)PC機(jī)與單片機(jī)組成的多機(jī)系統(tǒng)完成測控任務(wù)。PC機(jī)因其豐富的軟硬件資源和友好的人機(jī)界面而被用作上位機(jī),而單片機(jī)則因其優(yōu)越的性價(jià)比和靈活的功能配置而被用作下位機(jī)。上位機(jī)和下位機(jī)...

分類:電子測量 時(shí)間:2020-10-21 閱讀:414 關(guān)鍵詞:基于Fusion系列FPGA器件實(shí)現(xiàn)水溫測控系統(tǒng)的設(shè)計(jì)FPGA器件

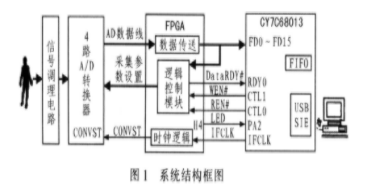

基于接口芯片與FPGA器件實(shí)現(xiàn)生物電信號數(shù)據(jù)采集的設(shè)計(jì)

1 引言 生物電信號是由生物體發(fā)出的不穩(wěn)定的微弱電信號,主要包括心電、肌電、腦電信號,其特點(diǎn)表現(xiàn)為信號弱、干擾強(qiáng)、 高。因此,在生物體的多參數(shù)測量中,高 尤...

時(shí)間:2020-08-14 閱讀:614 關(guān)鍵詞:基于接口芯片與FPGA器件實(shí)現(xiàn)生物電信號數(shù)據(jù)采集的設(shè)計(jì)芯片,FPGA器件

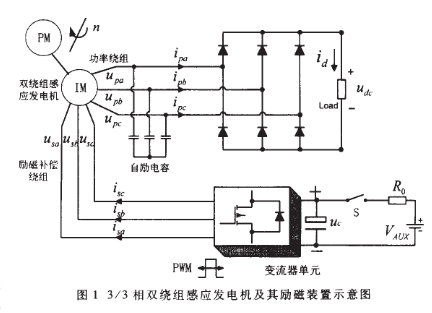

采用DSP和FPGA器件實(shí)現(xiàn)電機(jī)勵(lì)磁控制系統(tǒng)的設(shè)計(jì)

介紹了針對3/3相雙繞組感應(yīng)發(fā)電機(jī)設(shè)計(jì)的勵(lì)磁系統(tǒng),該系統(tǒng)由DSP和FPGA構(gòu)成。給出了控制系統(tǒng)的接口電路和實(shí)驗(yàn)結(jié)果。 1 、系統(tǒng)簡介 3/3相雙繞組感應(yīng)發(fā)電機(jī)帶有兩個(gè)繞組...

分類:工業(yè)電子 時(shí)間:2020-04-14 閱讀:795 關(guān)鍵詞:采用DSP和FPGA器件實(shí)現(xiàn)電機(jī)勵(lì)磁控制系統(tǒng)的設(shè)計(jì)DSP,電機(jī)

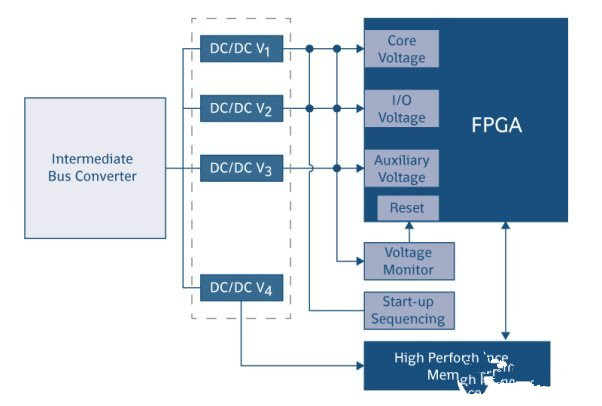

應(yīng)用于FPGA器件中電源模塊的選擇及設(shè)計(jì)方案

描述電源系統(tǒng)的需求很容易,執(zhí)行這些需求卻更具挑戰(zhàn)性。只要它比上一代產(chǎn)品更小、更可靠、更有效且成本更低,那么設(shè)計(jì)經(jīng)理、營銷團(tuán)隊(duì)和用戶就會很高興。FPGA等現(xiàn)代半導(dǎo)體器...

分類:電源技術(shù) 時(shí)間:2020-03-04 閱讀:658 關(guān)鍵詞:FPGA器件,電源模塊

FPGA器件在物聯(lián)網(wǎng)應(yīng)用程序中發(fā)展

隨著物聯(lián)網(wǎng)應(yīng)用程序的采用勢頭越來越大,嵌入式開發(fā)社區(qū)面臨的壓力也越來越大,以便兼顧每種設(shè)計(jì)的可用計(jì)算資源,延遲,成本和大小。由于其實(shí)時(shí)性,對云連接的關(guān)注也被視為一些發(fā)展的挑戰(zhàn),導(dǎo)致混合“霧”計(jì)算方法。...

分類:物聯(lián)網(wǎng)技術(shù) 時(shí)間:2019-03-15 閱讀:2240 關(guān)鍵詞:FPGA器件在物聯(lián)網(wǎng)應(yīng)用程序中發(fā)展物聯(lián)網(wǎng)

基于DSP技與+FPGA器件實(shí)現(xiàn)數(shù)據(jù)采集設(shè)備的小型化

引言 數(shù)據(jù)采集設(shè)備是測試系統(tǒng)中不可缺少的一部分,數(shù)據(jù)采集需要針對不同類型的需求,需要有高速A/D、低速A/D、數(shù)字多用表等功能,傳統(tǒng)數(shù)據(jù)采集設(shè)備是用一種儀器進(jìn)行一類測試,通過多種儀器組合實(shí)現(xiàn)一組完整測試,這...

分類:單片機(jī)與DSP 時(shí)間:2019-01-11 閱讀:163 關(guān)鍵詞:基于DSP技與+FPGA器件實(shí)現(xiàn)數(shù)據(jù)采集設(shè)備的小型化DSP,FPGA器件

主要FPGA供應(yīng)商已經(jīng)開始銷售集成了硬核處理器內(nèi)核的低成本FPGA器件,SoC類FPGA器件最終會成為主流。為能夠充分發(fā)揮所有重要FPGA的靈活性,這些器件提供了FPGA設(shè)計(jì)人員和軟...

分類:EDA/PLD/PLC 時(shí)間:2012-11-07 閱讀:2445 關(guān)鍵詞:SoC類FPGA器件設(shè)計(jì)難題解決方案SoCFPGACortex-A9

NXP新款CGV高速轉(zhuǎn)換器演示板采用LatticeECP3 FPGA器件

恩智浦半導(dǎo)體(NXP Semiconductors)近日宣布,CGV高速數(shù)據(jù)轉(zhuǎn)換器系列新增兩款低成本、低功耗演示板,新產(chǎn)品采用了萊迪思半導(dǎo)體公司生產(chǎn)的LatticeECP3器件。新演示板旨在證明...

分類:EDA/PLD/PLC 時(shí)間:2010-06-01 閱讀:4138 關(guān)鍵詞:NXP新款CGV高速轉(zhuǎn)換器演示板采用LatticeECP3 FPGA器件FPGA器件轉(zhuǎn)換器

Actel推出智能型混合信號FPGA器件SmartFusion

愛特公司(Actel Corporation)宣布推出世界智能型混合信號FPGA器件SmartFusion,該產(chǎn)品現(xiàn)正投入批量生產(chǎn)。SmartFusion器件帶有Actel經(jīng)過驗(yàn)證的FPGA架構(gòu),該架構(gòu)包括基于ARM ...

分類:EDA/PLD/PLC 時(shí)間:2010-03-09 閱讀:3416 關(guān)鍵詞:Actel推出智能型混合信號FPGA器件SmartFusionFPGA器件

愛特公司(ActelCorporation)宣布推出世界首個(gè)智能型混合信號FPGA器件SmartFusion,該產(chǎn)品現(xiàn)正投入批量生產(chǎn)。SmartFusion器件帶有Actel經(jīng)過驗(yàn)證的FPGA架構(gòu),該架構(gòu)包括基于ARMCortex-M3硬核處理器的

分類:EDA/PLD/PLC 時(shí)間:2010-03-05 閱讀:3550 關(guān)鍵詞:Actel推出世界首個(gè)智能型混合信號FPGA器件FPGA

0引言 邊緣檢測技術(shù)是圖像處理的一項(xiàng)基本技術(shù),在工業(yè)、航天、醫(yī)學(xué)、軍事等領(lǐng)域中有著廣泛的應(yīng)用。邊緣檢測算法的實(shí)現(xiàn)涉及復(fù)雜的計(jì)算步驟,故對處理速度有較高要求。采...

分類:EDA/PLD/PLC 時(shí)間:2009-10-30 閱讀:2599 關(guān)鍵詞:基于FPGA器件的Sobel算法實(shí)現(xiàn)FPGA器件

CPLD和FPGA都支持邊界掃描(JTAG)模式,JTAG端口用于邊界掃描測試、器件配置、應(yīng)用診斷等,符合IEEE 1532/IEEE 1149,1規(guī)范。每個(gè)CPLD/FPGA器件都有專用的JTAG端口,JTAG端口有4個(gè)引腳,具體描述見表1。 通過JTA...

分類:EDA/PLD/PLC 時(shí)間:2008-12-08 閱讀:3794 關(guān)鍵詞:CPLD/FPGA器件的配置方法1149CPLDFPGA

實(shí)現(xiàn)PLD器件功能最關(guān)鍵的技術(shù)是計(jì)算機(jī)輔助設(shè)計(jì)(CAD)。CAD技術(shù)和設(shè)計(jì)軟件及開發(fā)環(huán)境對于 CPLD/FPGA的設(shè)計(jì)至關(guān)重要,尤其是FPGA器件更依賴于開發(fā)軟件,CPLD/FPGA器件廠商都推出了自己的集成 開發(fā)環(huán)境(IDE),Xilinx...

分類:EDA/PLD/PLC 時(shí)間:2008-12-08 閱讀:2578 關(guān)鍵詞:CPLD/FPGA器件的開發(fā)過程CPLDFPGA

低功耗FPGA器件簡化了航天系統(tǒng)的設(shè)計(jì)

低功耗、可重編程的RT ProASIC3器件簡化了航天系統(tǒng)的設(shè)計(jì) 為了繼續(xù)提供滿足航天設(shè)計(jì)人員需求的創(chuàng)新硅解決方案,Actel宣布推出業(yè)界面向太空飛行應(yīng)用以Flash為基礎(chǔ),耐輻射的FPGA器件。全新的低功耗RT ProASIC?3器...

分類:通信與網(wǎng)絡(luò) 時(shí)間:2008-09-25 閱讀:1709 關(guān)鍵詞:低功耗FPGA器件簡化了航天系統(tǒng)的設(shè)計(jì)FPGA

Xilinx FPGA器件的去耦網(wǎng)絡(luò)設(shè)計(jì)范例

在設(shè)計(jì)XilinxFPGA器件去耦網(wǎng)絡(luò)時(shí),首先需要用ISE1O的設(shè)計(jì)工具規(guī)劃器件的每個(gè)輸入/輸出塊(Bank)的SSO(SimultaneouslySwitchingOutput,同步轉(zhuǎn)換輸出)個(gè)數(shù),因?yàn)镾SO是造成地線反彈和交調(diào)干擾的根源,每個(gè)B

分類:EDA/PLD/PLC 時(shí)間:2008-09-16 閱讀:2530 關(guān)鍵詞:Xilinx FPGA器件的去耦網(wǎng)絡(luò)設(shè)計(jì)范例FPGA器件去耦網(wǎng)絡(luò)

在配置FPGA器件時(shí)的常見問題及其解決方法。 (1)當(dāng)模式改變后,同時(shí)需要修改產(chǎn)生位流文件中的配置時(shí)鐘的屬性為CCLK或JTAGClock,否則無法配置。 (2)DONE狀態(tài)腳始終為低解決方法:檢查該引腳的負(fù)載是否太重,選...

分類:EDA/PLD/PLC 時(shí)間:2008-09-16 閱讀:2795 關(guān)鍵詞:配置FPGA器件時(shí)的常見問題FPGA器件

Xilinx的FPGA器件配置流程共有4個(gè)階段,每個(gè)階段分別執(zhí)行不同的命令和操作。這4個(gè)階段分別為配置存儲器清除、初始化、裝入配置數(shù)據(jù)和啟動器件,下面以Spartan-3的加載為例說明這個(gè)過程。 (1)配置存儲器清除階段(...

分類:EDA/PLD/PLC 時(shí)間:2008-09-16 閱讀:2067 關(guān)鍵詞:FPGA器件配置流程FPGA器件

只有成功配置可編程邏輯器件FPGA之后,器件才能正常工作。Xilinx FPGA的配置有3種模式,分別為并行(SelectMap)、串行(Serial)和邊界掃描(Boundary Scan)模式。當(dāng)然Virtex-5和Spartan-3E/3A的器件有更多的配置模式,...

分類:EDA/PLD/PLC 時(shí)間:2008-09-16 閱讀:3360 關(guān)鍵詞:FPGA器件配置模式XC17FPGA器件

- 高速PCB阻抗控制核心實(shí)操規(guī)范

- 高速數(shù)字系統(tǒng)(如DDR、SerDes)中的信號完整性濾波

- MOSFET在UPS電源中的應(yīng)用解析

- 電源管理IC在物聯(lián)網(wǎng)設(shè)備中的應(yīng)用

- SMT連接器焊接缺陷分析

- MOSFET在汽車電子中的應(yīng)用要求

- 通信設(shè)備電源管理IC應(yīng)用解析

- 通信設(shè)備連接器選型與設(shè)計(jì)

- PCB電磁兼容性(EMC)設(shè)計(jì)核心實(shí)操規(guī)范

- 物聯(lián)網(wǎng)節(jié)點(diǎn)低功耗設(shè)計(jì):信號鏈中的濾波與功耗管理